# Implementing Video Image Processing Algorithms on FPGA

## Video Image Processing and Computer Vision

#### Video Image Processing

- Video in and out

- Gamma correction

- Color balancing

- Noise removal

- Image sharpening

#### Implementing Image Pipeline in a Processor based on Da Vinci™ Technology

#### Computer Vision

- Feature matching, and extraction

- Object detection and recognition

- Object Tracking and motion estimation

- Dynamic resolution scaling

- Focus assessment

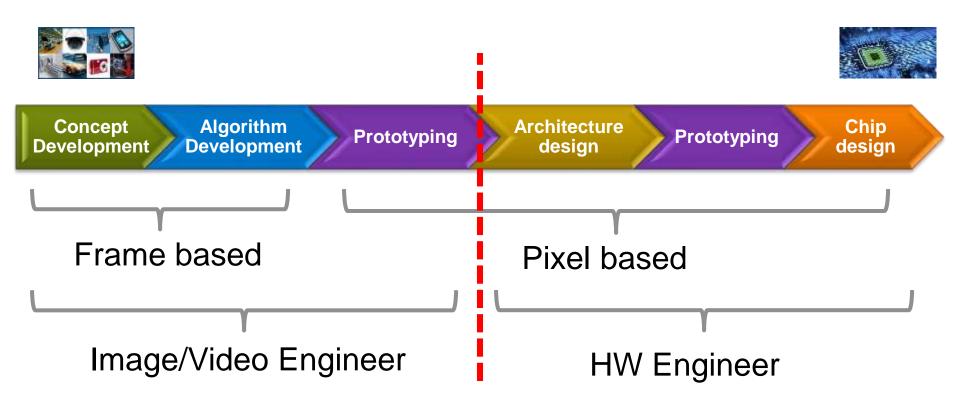

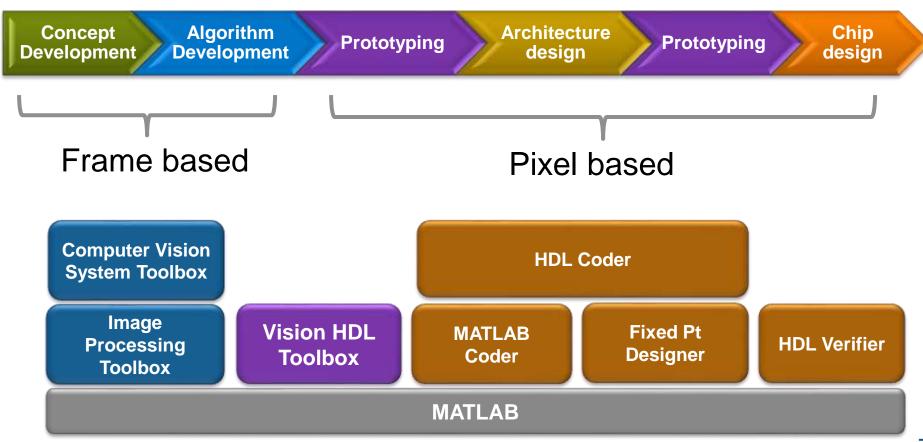

### **Workflow for Video Image Processing**

# Challenges in Design and Prototyping for Video and Image

#### Modeling video image processing systems

- ✓ Pixel-streaming behavior

- Code generation ready model

- Prototyping and concept proofing

- ✓ Technology independent code

**Hardware Engineer**

# Prototyping and Designing FPGA and ASIC for video and image processing algorithms

- ✓ Portable, readable and efficient IP Cores

- Flexible architecture and controllable latency

- ✓ FPGA-in-the-loop testing using ML and SL as frame based test bench

#### **Vision HDL Toolbox**

#### Design and prototype video image processing systems

- Modeling hardware behavior of the algorithms

- Pixel-based functions and blocks

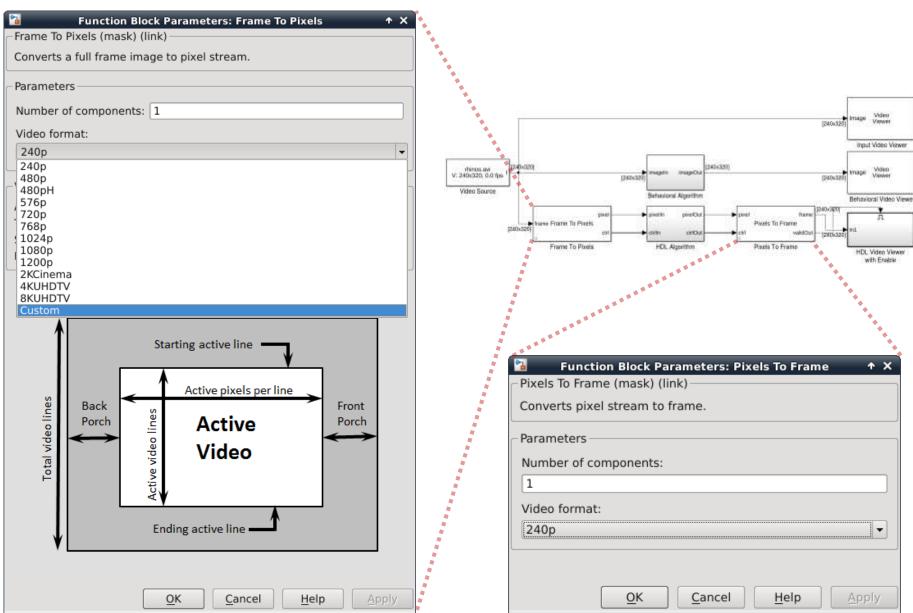

- Conversion between frames and pixels

- Standard and custom frame sizes

- Prototyping algorithms on hardware

- (With HDL Coder) Efficient and readable HDL code

- (With HDL Verifier) FPGA-in-the-loop testing and acceleration

## **Pixel Based Video Image Algorithms**

#### Analysis & Enhancement

Edge Detection, Median Filter

#### Conversions

- Chroma Resampling, Color-Space Converter

- Demosaic Interpolator, Gamma Corrector, Look-up Table

#### Filters

Image Filter, Median Filter

#### Morphological Operations

- Dilation, Erosion,

- Opening, Closing

#### Statistics

- Histogram

- Image Statistics

#### I/O Interfaces

Frame to Pixels, Pixels to Frame, FIL versions

#### Utilities

- Pixel Control Bus Creator

- Pixel Control Bus Selector

### A Complete Solution for Embedded Vision

# A Complete Solution for Embedded Vision

| Product                        | Capabilities                                                                                            |

|--------------------------------|---------------------------------------------------------------------------------------------------------|

| Vision HDL Toolbox             | Design and simulate image processing, video, and computer vision systems for FPGAs and ASICs            |

| HDL Coder                      | Provide RTL code and testbench generation capability for the functions and blocks in Vision HDL Toolbox |

| HDL Verifier                   | Provide FPGA-in-the-loop capability for Vision HDL Toolbox                                              |

| Computer Vision System Toolbox | Provide frame based computer vision functions and blocks as well as image and video I/O capability      |

| Image Processing Toolbox       | Provide image processing and analysis functions                                                         |

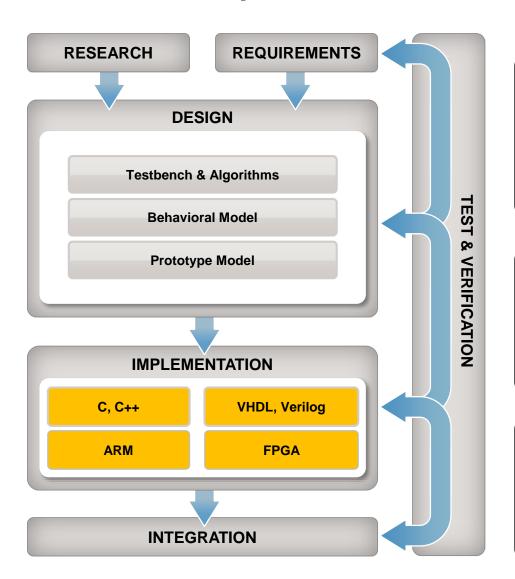

# Model-Based Design For Embedded Vision

#### From Concept to Production

- Build behavioral model for fast simulation and testing

- Convert to prototype model for targeting hardware

- Generate efficient code

- Explore and optimize implementation tradeoffs

- Automate regression testing

- Detect design errors

- Support certification and standards

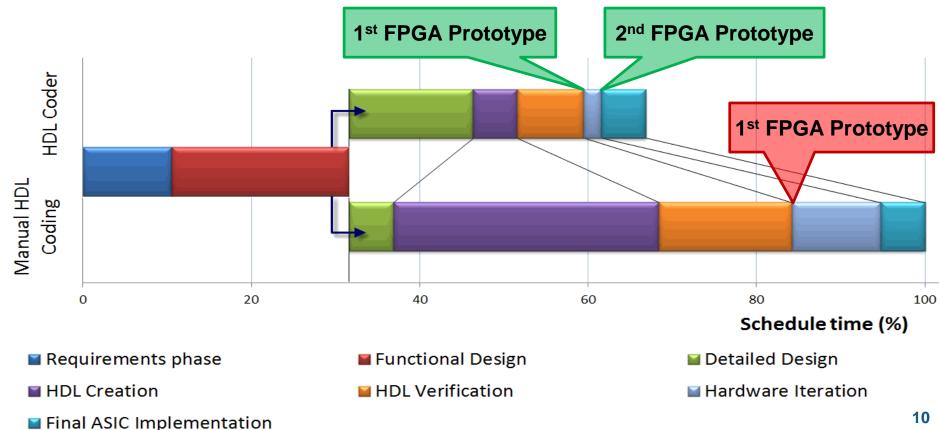

# **ROI: Customer Adoption Of Model-Based Design**

#### Time spent on FPGA implementation

- Shorter implementation time by 48% (total project 33%)

- Reduced FPGA prototype development schedule by 47%

- Shorter design iteration cycle by 80%

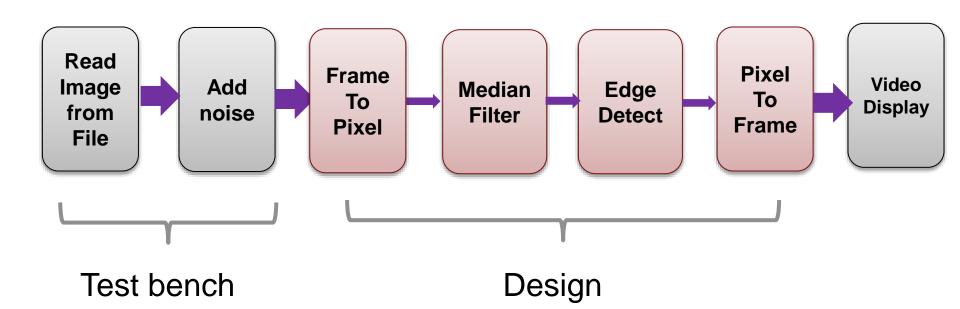

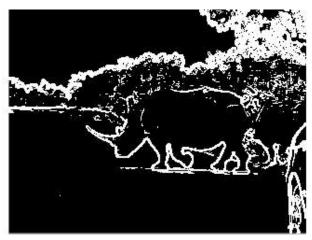

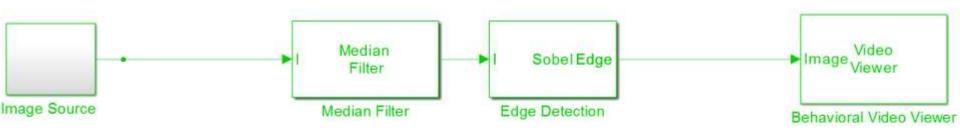

## **Demo: Enhanced Edge Detection**

### **Enhanced Edge Detection**

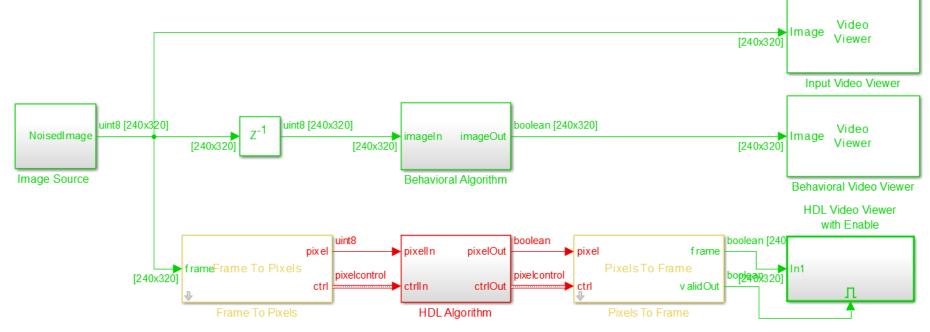

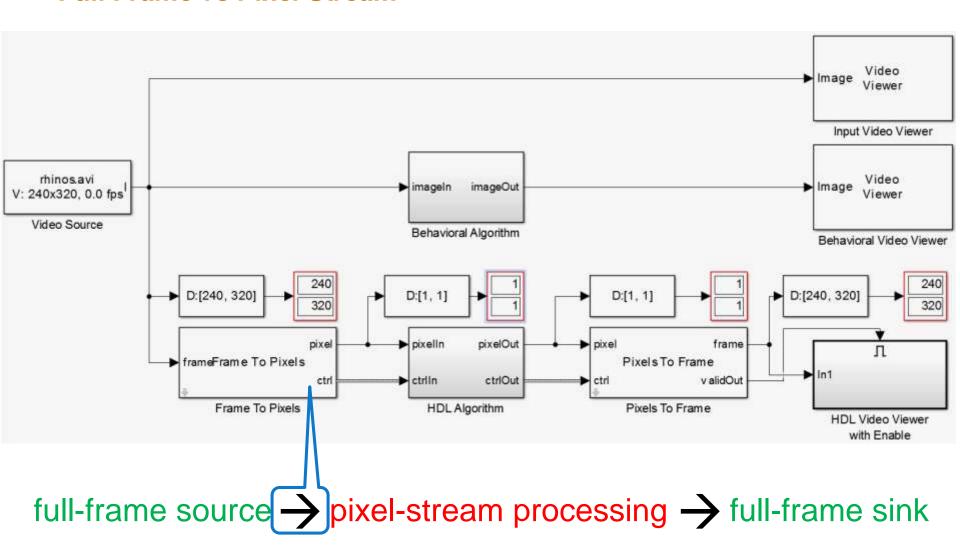

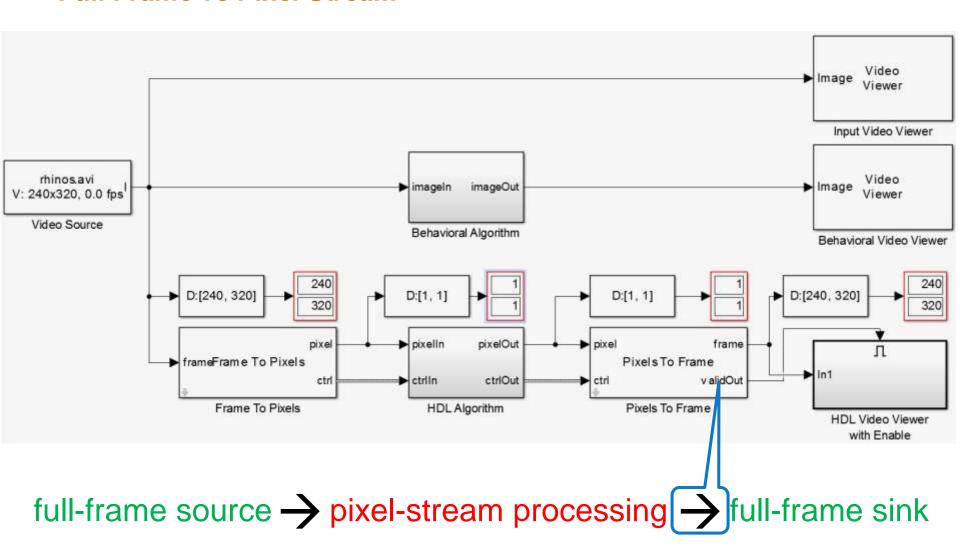

### **Streaming Pixel Interface**

Full Frame vs Pixel Stream

### **Streaming Pixel Interface**

Full Frame vs Pixel Stream

#### Frame To Pixels and Pixels To Frame

## **Examples: Starting Points for Your Models**

#### **▼ Simulink Examples**

#### ▼ Matlab Examples

#### Pixel-Streaming Design in MATLAB

Uses: Matlab, Computer Vision System Toolbox

#### Accelerate a Pixel-Streaming Design Using MATLAB Coder

Uses: Matlab, Computer Vision System Toolbox, Matlab Coder

#### Enhanced Edge Detection from Noisy Color Video

Uses: Matlab, Computer Vision System Toolbox, Matlab Coder

## **Image Filtering**

Keywords: Median Filter, Image Filter, PSNR

Median Filter

#### Image Filtering Using Vision HDL Blocks Verification imageMatrix matrixIn Ref Ref Out Image Source HDL Full-Frame Behavioral Model pix el pix ell n pixelOut **▶** pix el frame IframeFrame To Pixels PixelsTo Frame Info v alidOut ▶ ctrlin ctrl ctrlOut Frame To Pixels Pixel-Stream HDL Model Pixels To Frame pixel pixel ▶pixel pixel Median Filter pix ell n Image Filter pixelOut 2 ctrl ► ctrl ctrl ► ctrl ctrlln drlOut

Image Filter

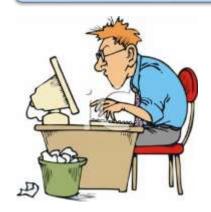

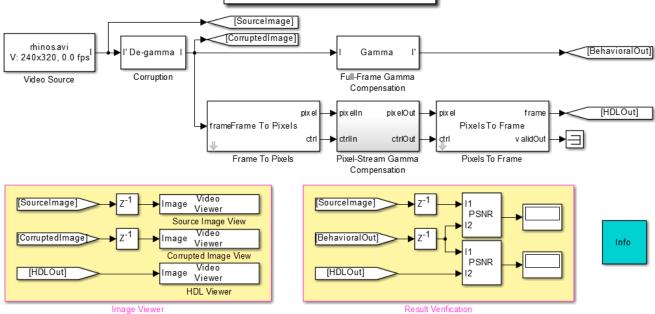

## **Gamma Correction Example**

#### Keywords: Gamma, PSNR

#### Gamma Correction

Copyright 2014 The MathWorks, Inc.

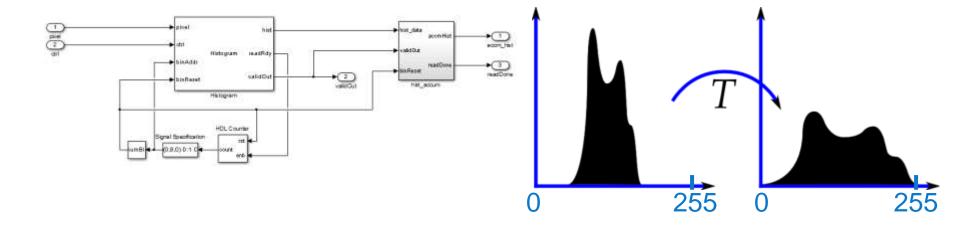

# **Histogram Equalization**

Keywords: Histogram, Linear Equalization, External Frame Delay

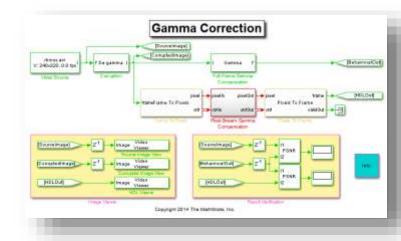

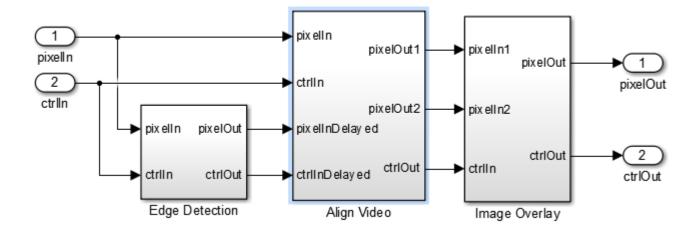

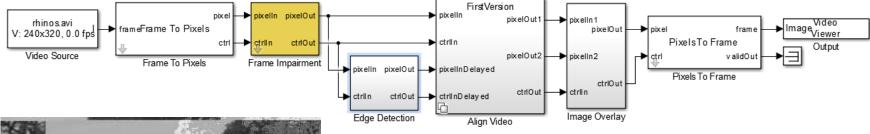

## **Edge Detection and Image Overlay**

Keywords: Sobel, Align Video, Alpha Mix, PSNR

### **Edge Detection with Impaired Frame**

Keywords: Sobel, Align Video, Alpha Mix, PSNR

#### Edge Detection and Image Overlay with Impaired Frame

Align Video is implemented as a variant subsystem.

To simulate using the FirstVersion variant, type VERSION=1 at MATLAB prompt.

To simulate using the SecondVersion variant, type VERSION=2 at MATLAB prompt.

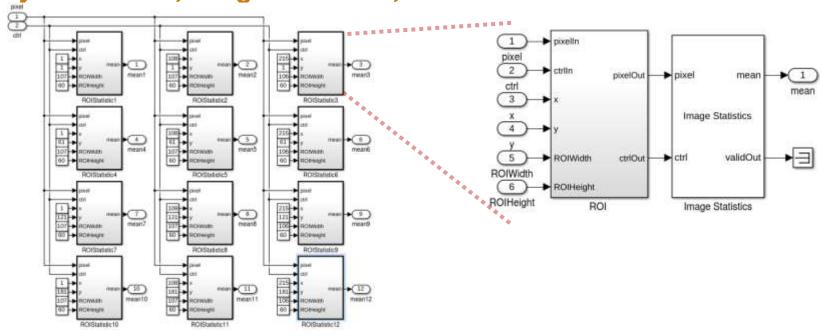

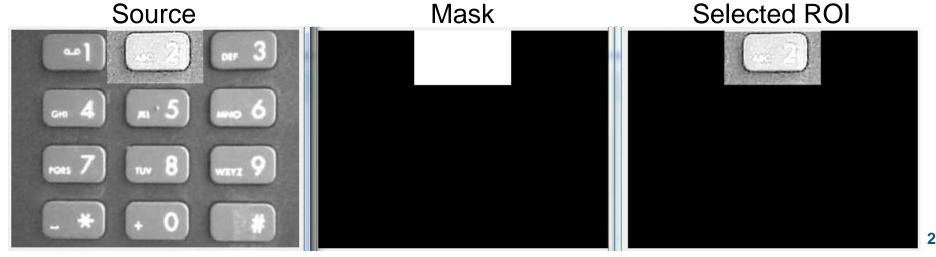

## **Multi-Zone Metering**

Keywords: ROI, Image Statistics, Mean

#### **HDL Coder**

Provides VHDL and Verilog code generation for MATLAB and Simulink

```

9);

9);

FILTER;

i);

ls that differ more than th_pix

Hz == ACC_STATE && validFilter == 1

th_pix_in

di = 0;

countAddi = 0;

elseif deltai < -th_pix_in

deltaAddi = 0;

countAddi = 0;

else

deltaAddi = deltai;

countAddi = 1;

end

Index = i;

MATLAB Code

```

10X more concise

HDL Coder

60% reduction in time to produce a working prototype

# **HDL Products Key Features**

- Code Generation

- Target-independent HDL Code

- IEEE 1376 compliant VHDL®

- IEEE 1364-2001 compliant Verilog®

- Verification

- Generate HDL test-bench

- Co-simulate with ModelSim and Incisive

- Design automation

- Synthesize using integrated Xilinx and Altera synthesis tool interface

- Optimize for area-speed

- Program Xilinx and Altera boards

MATLAB® and Simulink® Algorithm and System Design

> HDL Coder HDL Verifier

HDL

FPGA

**ASIC**

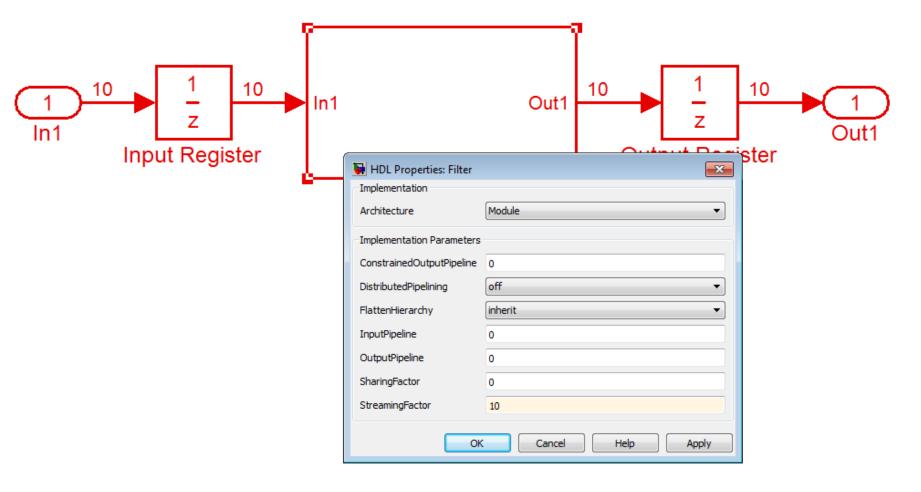

# **HDL Coder: Key Features and Options**

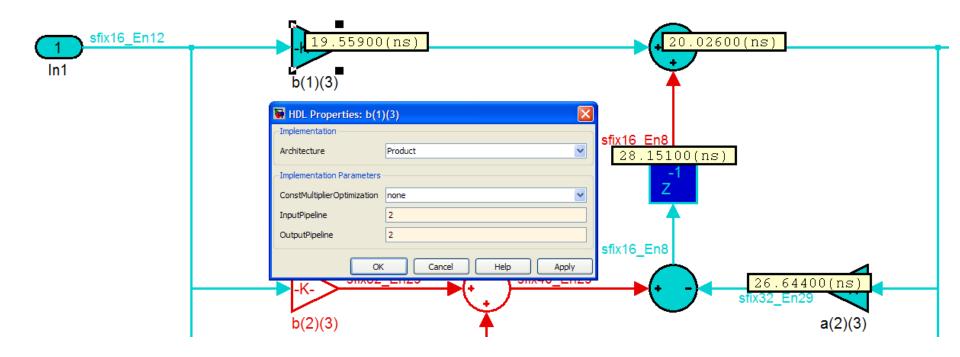

#### Area Optimizations

- Simulink

- Streaming

- Sharing

- Line buffers as RAMs

- RAM Fusion

- Architecture Flattening

- MATLAB

- RAM Mapping

- Loop Streaming

- Resource Sharing

- CSD/FCSD

#### **Speed Optimizations**

- Simulink

- Input/Output pipelining

- Distributed Pipelining

- Hierarchical Dist. Pipelining

- Constrained Pipelining

- Back-Annotation

- MATLAB

- Input/Output pipelining

- Distributed pipelining

- Loop Unrolling

#### Validation and Verification

- Automatic Delay Balancing

- Validation model generation

# **Hardware Design Solution:**

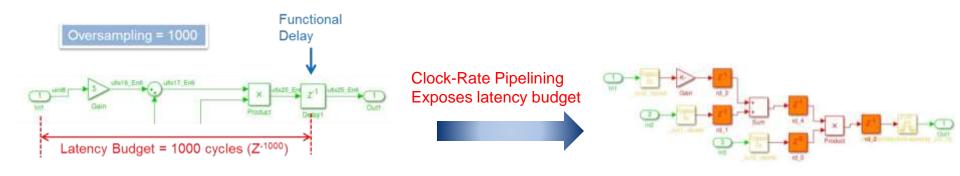

# Identifying the critical path

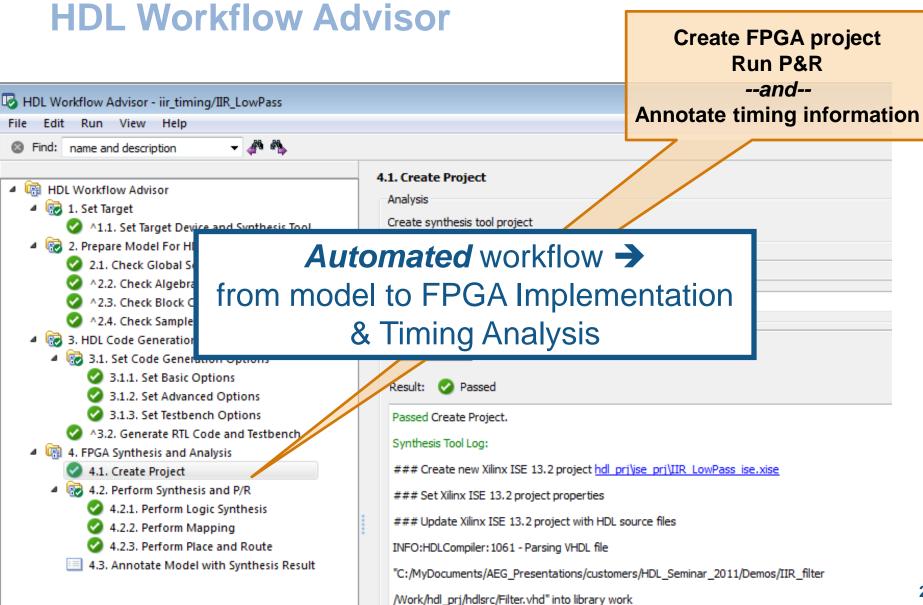

## **Integrating with P&R Timing Analysis**

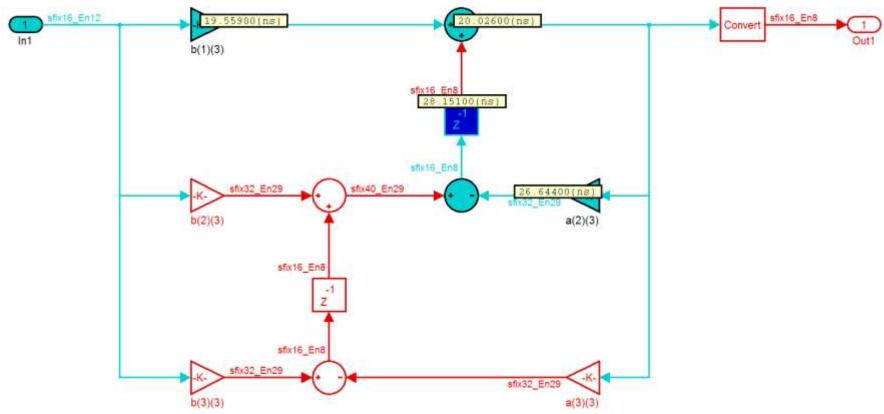

#### Critical Path highlighting:

- Visual representation of critical path in your model

- Easier to identify bottlenecks of your model

# **Meeting Timing Constraint**

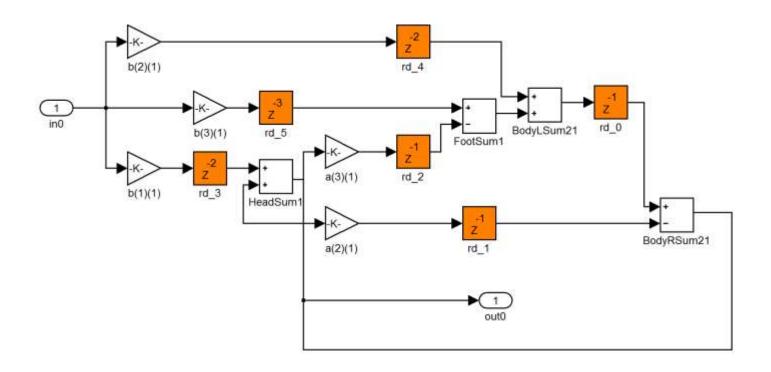

# **Distributed Pipelining**

# **Distributed Pipelining**

## **Speed Optimization**

- Distributed pipelining (model retiming)

- Automatic delay compensation where needed

- Constrained retiming gives you more influence

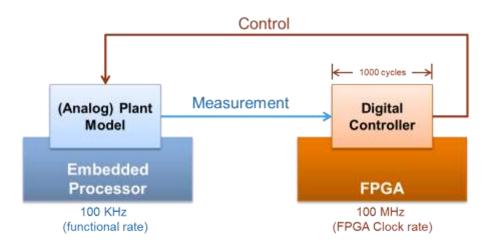

## **Clock-Rate Pipelining**

#### **Critical Path Estimation**

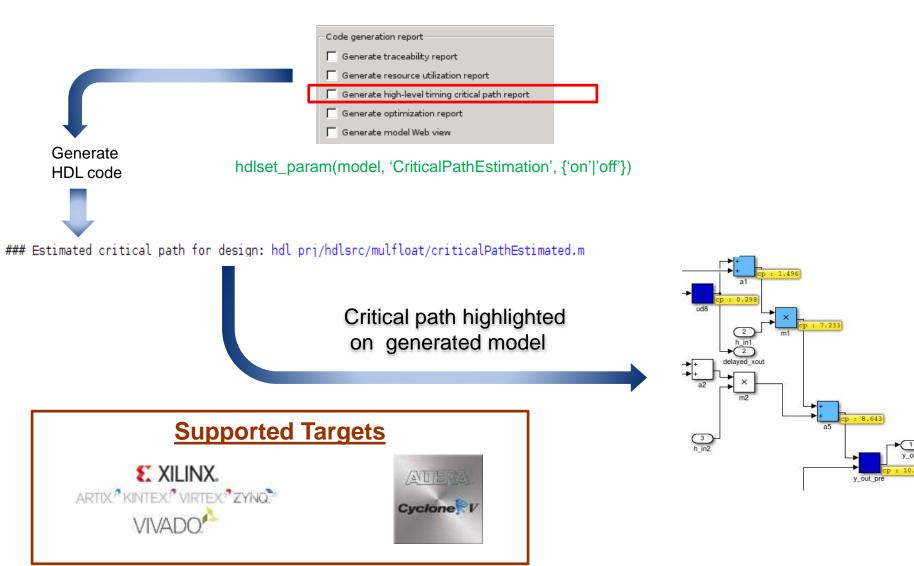

# **Meeting Resource Constraint**

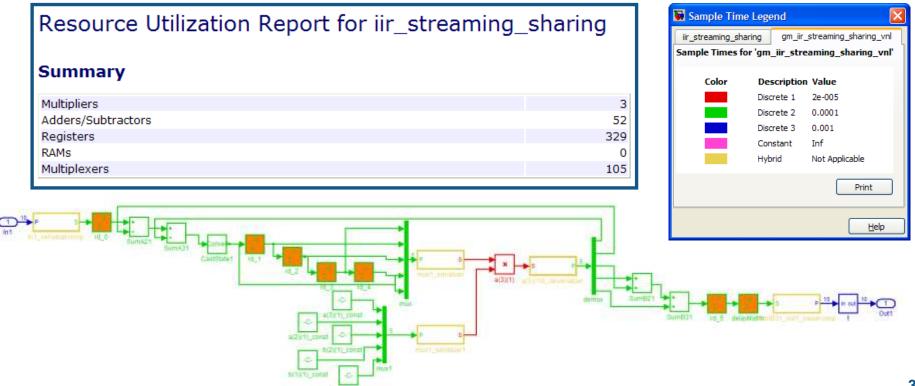

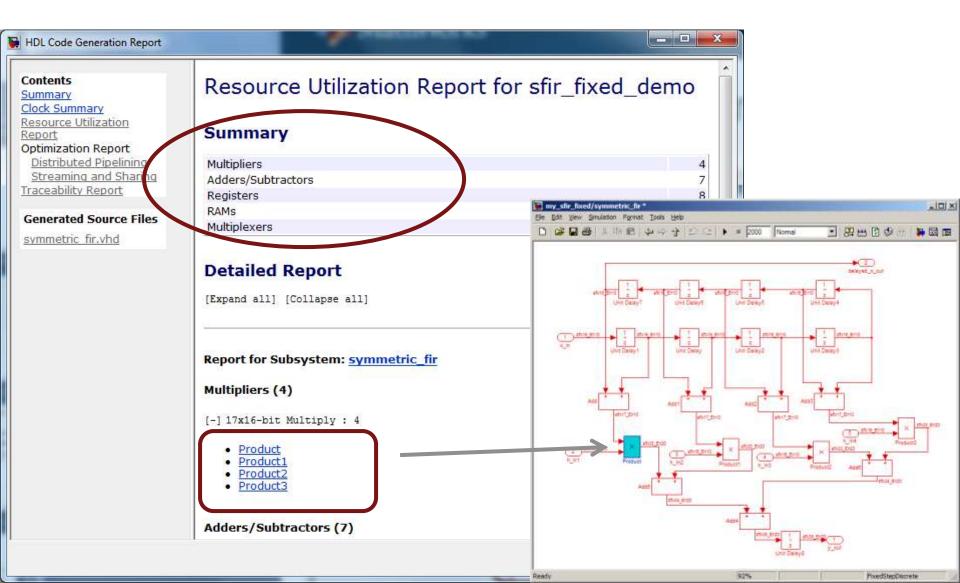

**Area Optimization**

# **Hardware Design Solution:**

# **Resource Sharing and Streaming**

# Resource Sharing and Streaming

#### **Area Optimization**

- Easily share <u>multipliers</u> and <u>identical subsystems</u>

- Direct feedback through resource utilization report

- Prove correctness through validation models

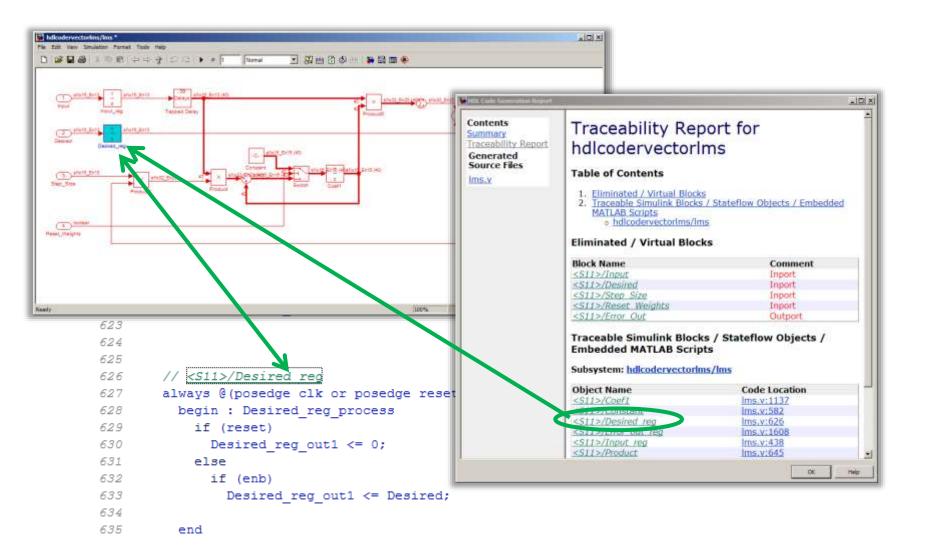

# **Traceability Between Model and Code**

### **Resource Utilization Estimation**

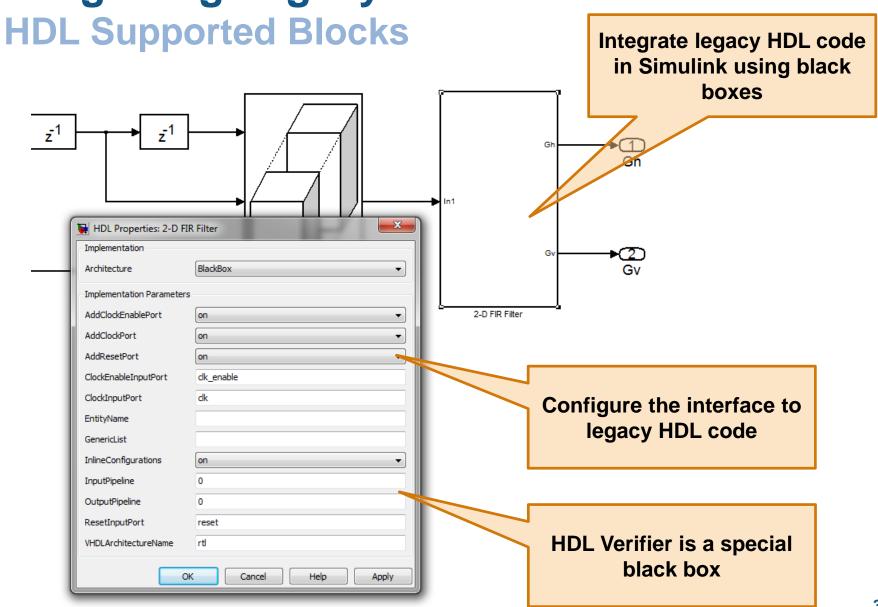

**Integrating Legacy HDL Code**

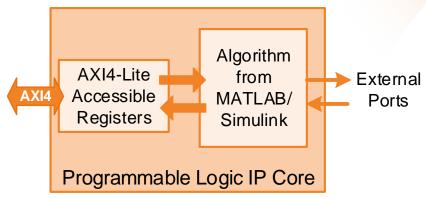

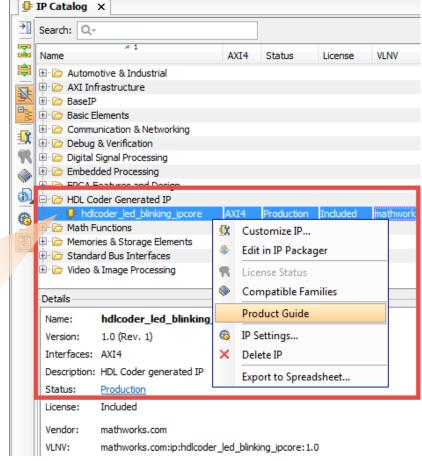

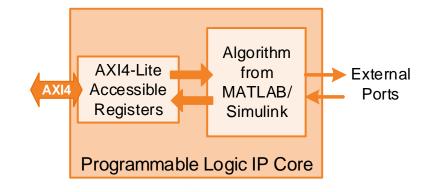

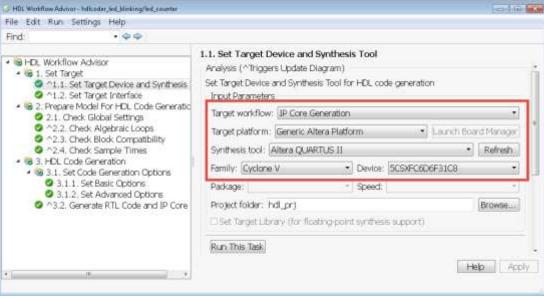

#### **Vivado IP Core Generation**

- Generate sharable and re-usable Vivado IP core from MATLAB/ Simulink HDL Workflow Advisor

- Support AXI4 interfaces to connect FPGA IP core to Zynq ARM processor

- Generate IP core report as IP Product Guide

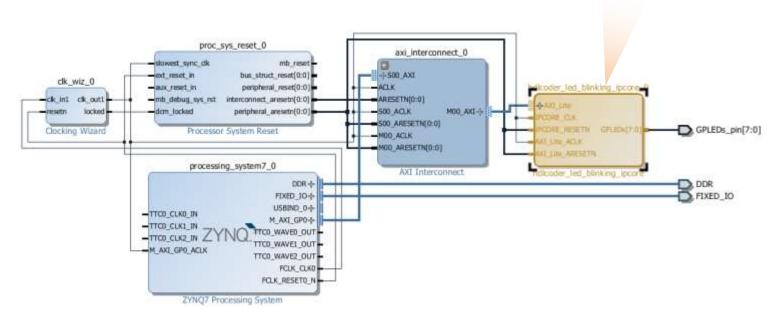

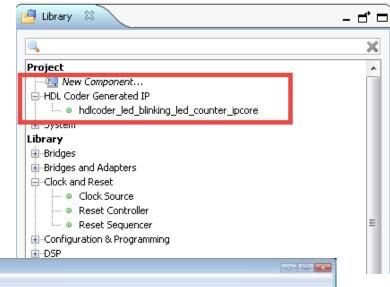

## Vivado IP Integrator Support for Zynq

- Integrate Xilinx Vivado IP

Integrator tool flow into HDL

Workflow Advisor

- Insert the generated IP core into Vivado Zynq system design

- Build and Program Zynq board

# Altera IP Core Generation + QSys Integration R2014b

- Generate sharable and re-usable Altera

IP from MATLAB/ Simulink HDL WFA

- Support AXI4 interfaces to connect FPGA

IP to Altera SoC ARM processor

- Generate IP core report as IP Data Sheet

- QSys integration for rapid prototyping

# **Backup**

# **CVST** and VHT, complimentary products

#### **Product details**

|                     | VHT                                                                                                   | CVST                                                                                                                                               |

|---------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Image<br>Processing | Pixel based                                                                                           | Frame based                                                                                                                                        |

| Workflow            | System prototyping                                                                                    | Algorithm design                                                                                                                                   |

| Algorithms          | Image filtering Color space conversion Edge detection Statistics & histogram Morphological operations | (Most of the VHT algorithms, plus) Object detection & tracking Feature extraction and matching Stereo vision Camera calibration Image registration |

| I/O                 | Frame-to-pixel Pixel-to-frame FIL                                                                     | File I/O<br>Video display                                                                                                                          |

| Code gen            | HDL (with HDL Coder)                                                                                  | C (with ML Coder or SL Coder)                                                                                                                      |

## MBD Workflow for Embedded Vision (video)

#### **MBD** workflow

- Build behavior model with CVST blocks and simulate

- 2. Build prototyping model with VHT blocks and simulate

- Generate HDL code using HDL Coder

- Run HDL code on FPGA and run testbench in SL (FIL)