Leonardo DRS Performs FPGA-Based Hardware-in-the-Loop Testing of Shipboard Power Electronics Systems

“With Simulink, Simscape, and HDL Coder, we can develop plant models and deploy them directly to an FPGA for HIL tests; it’s a no-nonsense, no-compromise way to simulate large-scale power electronics systems.”

Challenge

Conduct high-fidelity, microsecond-scale hardware-in-the-loop tests of shipboard power electronics systems and control software

Solution

Use Simulink, Simulink Real-Time, Simscape Electrical, and HDL Coder to model power electronics designs and perform microsecond-scale real-time HIL simulations on FPGA hardware

Results

- Design iterations reduced from days to hours

- Cost, time, and lab space saved

- Simulation models reused for HIL testing

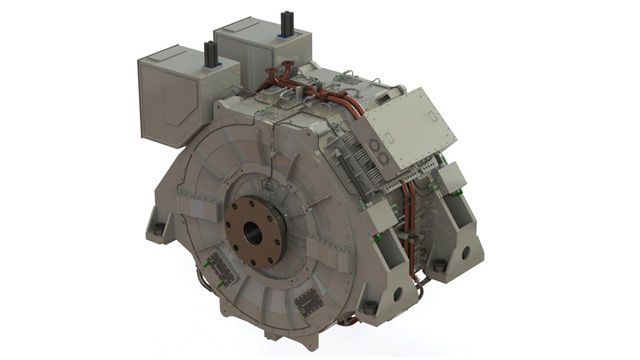

Large propulsion motor.

Power electronics systems on large ships act as multimegawatt microgrids, powering propulsion and all other onboard electrical equipment. These systems often require multimillion-dollar investments and a year or more to build. As a result, engineering teams that develop the control software often lack access to feature-complete hardware until late in development.

Leonardo DRS engineers use MATLAB® Simulink®, Simscape Electrical™, Simulink Real-Time™, and HDL Coder™ to model shipboard power electronics systems and perform real-time hardware-in-the-loop (HIL) tests on an FPGA module in Speedgoat real-time target hardware.

“Using the HIL workflow we implemented with MATLAB and Simulink, we ensure that our equipment will perform the way we expect in the customer environment for a fraction of the cost of setting up physically equivalent hardware and additional testing infrastructure,” says Chris Harper, electrical systems engineer at Leonardo DRS. “We can test day or night, with or without hardware, while reducing the chances of damage to a full-scale system.”

Challenge

Due to the large scale of Leonardo DRS power electronics systems, engineers previously relied on small-scale prototypes and hardware test beds that were not feature-complete. This approach made it difficult to test the complete range of software interactions with the hardware. When full-scale hardware did become available, testing time was limited because multiple internal and customer teams needed to access it. Further, tests on the hardware had to be designed and orchestrated to avoid damaging the equipment or endangering personnel.

HIL testing would enable Leonardo DRS engineers to safely conduct comprehensive software tests. However, CPU-based HIL setups running C code were not capable of simulations with microsecond sampling times at the required level of fidelity. One commercially available FPGA-based HIL solution that the team evaluated required extensive HDL programming, even for relatively simple power electronics designs. Leonardo engineers needed to run high-fidelity, microsecond-scale HIL testing on power electronics designs without hand-coding HDL.

Solution

Leonardo DRS established a workflow for power electronics HIL simulation based on Simulink, Simscape Electrical, Simulink Real-Time, HDL Coder, and Speedgoat real-time target hardware.

In this workflow, the engineering team develops a high-level plant model in Simulink that includes sources, loads, IGBTs, and other component blocks from Simscape Electrical.

They perform open-loop simulations with this plant model to verify that the high-level design meets system requirements. They also use the plant model to run closed-loop simulations with a Simulink model of the controller to validate controller functionality.

As the hardware design progresses, the team refines and adds detail to the plant model. For example, they replace generic IGBT blocks with blocks parameterized for the specific IGBT components chosen for the design.

Next, the team prepares the model for deployment to the FPGA on the real-time HIL target machine. This process includes identifying and replacing nonlinear elements of the model with switched linear equivalents. “Because we sample at one-microsecond rates and our dead time is so small, we don’t really care about nonlinearities in the system—we get all the accuracy we need from switched linear components,” says Henry Brengel, software engineer at Leonardo DRS.

After running simulations to ensure that the updated plant model exhibits the same dynamic behavior as earlier models, the team uses the Simscape HDL Workflow Advisor with Simulink Real-Time and HDL Coder to generate HDL code from the model and deploy it to the FPGA module of the Speedgoat real-time target hardware.

If it becomes necessary to reduce FPGA resource utilization, the team replaces switched linear blocks with average value blocks. Lowering the model fidelity in this way enables HIL tests to run at 50-nanosecond sampling times.

Leonardo DRS engineers are using the new HIL workflow on production projects, and they are extending it to include fault testing and replication of issues identified on deployed power systems.

Full-scale version of a power conversion system analyzed in real time.

Results

- Design iterations reduced from days to hours. “Debugging and resolving issues on real equipment can easily take a week because our access to it is so limited,” says Brengel. “Now, engineers can resolve those same issues in a few hours because they have immediate access to the Simulink based HIL setup, and there’s no risk of damaging the costly system components.”

- Cost, time, and lab space saved. “The HIL testbench we create using Simulink, Simscape Electrical, and HDL Coder replaces equipment that would cost millions of dollars, take six months or a year to procure, and consume a huge area in our lab,” says Harper. “We can test software and control hardware for a multimillion-dollar plant in real time—without the plant and at a fraction of the cost.”

- Simulation models reused for HIL testing. “Our engineers excel at power electronics design but are not experts in HDL programming,” says Harper. “With Simulink, they don’t have to be. They can use the same models they trust and run simulations with every day to run HIL tests on an FPGA, without manually translating them into another language.”