Wolfson Microelectronics Accelerates Audio Hub Design Verification

“For development of the world’s first highly optimized digital audio hub solution, Simulink and HDL Coder were the best options. The design and verification flow we applied using MathWorks tools scales well and provides the route to build more complex DSP and signal mixing paths.”

Challenge

Solution

Results

- Months of hand-coding eliminated

- Datapath verification coverage increased to 100%

- Debugging process accelerated by 20%

Originally, the audio ICs in mobile devices were predominantly stereo codecs with standard analog-to-digital (ADC) and digital-to-analog (DAC) paths. Smartphones now require audio architectures that support multiple path configurations and audio sources, including headsets, voice channels, MP3 audio, and radio tuners.

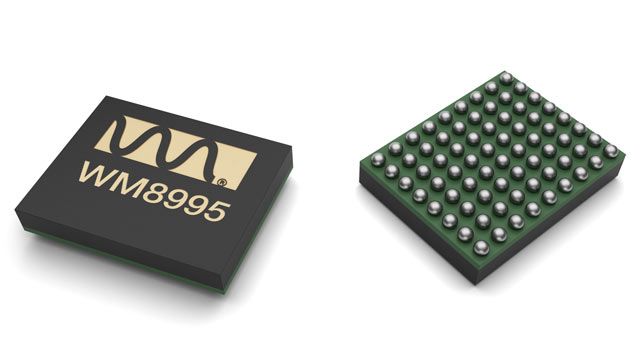

To address these requirements, Wolfson Microelectronics, now part of Cirrus Logic, Inc., has developed the world’s first category-defining digital audio hub solution for mobile phones, the WM8995. The WM8995 enables system designers to optimally manage multiple concurrent audio uses, which means the consumer can take a hands-free call over a Bluetooth headset, listen to music, and receive navigation commands, all at the same time and on the same handset.

Wolfson engineers used MATLAB® and Simulink® to design and simulate these advanced, multipath audio hubs and used HDL Coder™ to generate bit-true Verilog® code to verify their digital signal processor (DSP) implementation.

“For analysis and datapath design, MATLAB and Simulink provide a much more powerful environment than hand-coding in C,” explains Brian Paisley, principal DSP engineer at Wolfson. “In addition, HDL Coder automates much of the generation of verification models, which shortens development time, improves quality, and increases our confidence in the design.”

Challenge

A common method for verifying single datapath designs involves running the high-level algorithm with a set of input vectors from a file and capturing the corresponding output vectors in a file to create a golden reference. The chip verification environment then applies the same input vectors and compares its resulting output with the golden reference.

This approach is acceptable for small designs but quickly becomes unworkable as design complexity increases. The multiple paths and use cases of Wolfson’s audio hubs necessitated a more powerful verification process that could support constrained random stimulus and dynamic modeling.

“The different setups, channel configurations, and paths that need to be tested on an audio hub would require many reference files, totaling several gigabytes of data. Generating and working with these files wasn’t an option,” says Gavin Wilson, senior design engineer at Wolfson.

Solution

Wolfson used MathWorks tools for Model-Based Design to model, simulate, and verify the design of its new audio hub.

In the initial stages, DSP engineers used MATLAB and Simulink to investigate potential algorithms and develop floating-point models of the design. Because Simulink had been used on many previous designs, the engineers could easily reuse their in-house library of highly optimized DSP functions, such as finite impulse response (FIR) and infinite impulse response (IIR) filters and equalizers. Using the powerful stimulus and analysis libraries in Simulink, multiple simulations were run on the models to ensure that the characteristics and performance of the floating-point implementation met the chip’s requirements.

Next, Fixed-Point Designer™ was used to convert the floating-point models to a fixed-point, bit-accurate design, which was passed to the digital engineers as an executable specification.

To ensure ultra-low power use, the algorithms were implemented in assembly language on a custom arithmetic logic unit (ALU).

Wolfson engineers verified the implementation by generating Verilog code from their existing Simulink models using HDL Coder. Within their Verilog environment, the team used this bit-accurate Verilog code as the dynamic model of the DSP implementation. Constrained random simulations were run on the entire device, verifying hundreds of scenarios against the Verilog models generated from Simulink. Fast Fourier transforms were automatically performed on the data as an additional level of verification.

Wolfson has developed a family of audio hub solutions that are designed to deliver world-class audio and performance for a vast range of digital consumer products.

Results

Months of hand-coding eliminated. “Manually coding the models for an audio hub project would typically have taken about 8 or 9 weeks,” says Paisley. “Using HDL Coder, we generated the Verilog in a day.”

Datapath verification coverage increased to 100%. “With Simulink and HDL Coder, we applied a constrained random verification technique that would have been impossible using golden reference files,” Wilson explains. “As a result, our datapath verification was able to hit 100% of the specified cover points.”

Debugging process accelerated by 20%. “In the past, debugging involved comparing simulation results from different tools,” says Wilson. “Now when datapath simulation mismatches occur, all the information needed to debug the problem is in a single environment. That has accelerated our debugging process by as much as 20%.”