Allegro MicroSystems Accelerates Chip Verification with MathWorks and Model-Based Verification

Kamel Belhous, Allegro MicroSystems

Sarah Brooks, Allegro MicroSystems

Sanjay Chatterjee, Allegro MicroSystems

Allegro MicroSystems collaborated with the MathWorks development and application engineering teams to enhance its model-based verification methodology for sensor ICs. Discover the significant benefits of this approach from insights shared by Kamel Belhous, director of engineering; Sarah Brooks, principal design engineer; and Sanjay Chatterjee, manager of design verification.

“We used a new methodology, which is about really porting the traditional verification techniques from constrained-random using UVM to the verification of the model and the architecture. The bugs that we found—early—were related to the architecture of the product.”—Kamel Belhous, director of engineering, Allegro MicroSystems

This customer story explores:

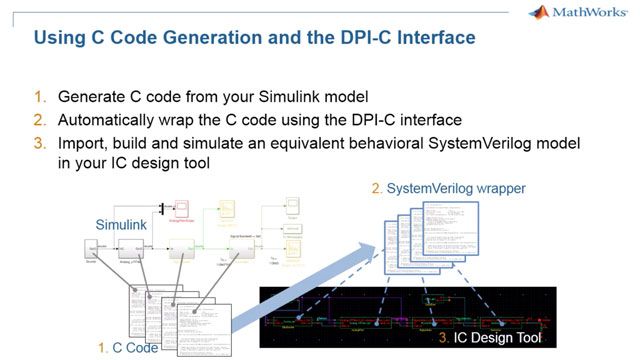

- Early Verification Initiatives: Learn how Allegro is implementing a “shift-left” strategy to verify chip architectures earlier in the development process, including mixed-signal interfaces.

- Enhanced Test Case Development: Understand how Allegro uses model-based verification to create more effective test cases tailored to the specific applications of its chips.

- Improved Collaboration: See how model-based verification fosters collaboration between product marketing, system design, hardware design, and verification teams.

Published: 3 Apr 2025