Design and Verification of FPGA and ASIC Applications

The development of electronic hardware can be a time-consuming and costly undertaking, with a significant proportion of the effort invested in verification. Recent developments in MATLAB® and Simulink® reduce the cost of developing FPGA and ASIC applications, through providing strong integration with conventional EDA workflows. This includes not only the efficient generation of RTL for implementation of algorithms, but also the generation of effective test benches to aid verification for both digital and mixed-signal systems. In this session, Graham demonstrates you how you can:

- Generate VHDL® or Verilog® code from MATLAB, Simulink, and Stateflow® for FPGA or ASIC implementation

- Develop system-level testbenches in MATLAB and Simulink, and reuse for RTL verification through cosimulation with EDA tools and through FPGA-in-the-loop methods

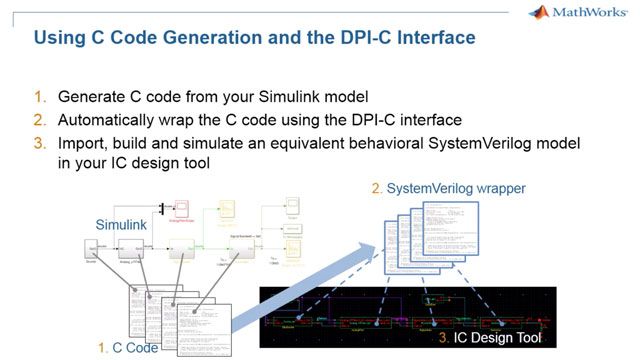

- Export models from MATLAB and Simulink to other verification environments, including SystemVerilog and SystemC/TLM

Recorded: 7 Oct 2014