HDL Coder Clock Rate Pipelining, Part 1: Introduction

Part one of this two-part series on clock rate pipelining discusses:

- Why clock rate pipelining is needed

- Why pipeline stages need to be inserted into designs that target an FPGA

- How sample rates in Simulink® map to clock rates on an FPGA

- How to use oversampling in HDL Coder™ to scale up Simulink data rates to faster FPGA clock rates

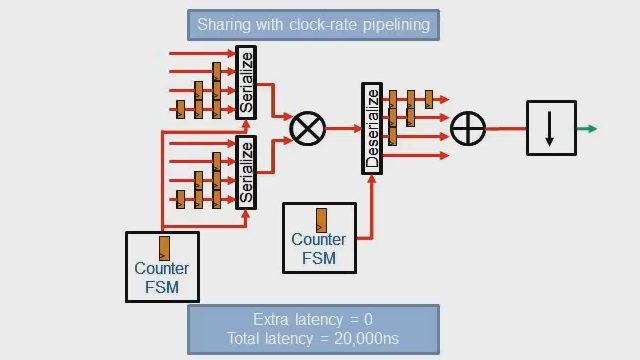

- How clock rate pipelining works

Part two of this series demonstrates how to combine clock rate pipelining with other HDL Coder optimizations to trade off speed versus resource usage.

Published: 25 May 2016