Integer-Output RS Decoder HDL Optimized

Decode data using Reed-Solomon (RS) decoder

Libraries:

Communications Toolbox HDL Support /

Error Detection and Correction /

Block

Description

The Integer-Output RS Decoder HDL Optimized block decodes data using RS decoder. The RS decoding follows the same standards as any other cyclic redundancy code. Use this block to model communications system forward error correction (FEC) codes. The block provides an architecture suitable for HDL code generation and hardware deployment.

For more information about the RS decoder, see the Integer-Output RS Decoder block. For more information on representing data for RS codes, see Integer Format (Reed-Solomon Only).

Examples

Using HDL Optimized RS Encoder/Decoder Library Blocks

Implement encoder and decoder for the IEEE® 802.16 standard by using HDL optimized Reed-Solomon (RS) encoder and decoder Simulink® blocks.

Ports

Input

Input data, specified as a scalar representing one symbol. For binary point

scaling, the input data type must be an unsigned integer or an unsigned fixed point.

The double data type is allowed for simulation, but not for HDL

code generation.

Data Types: double | uint8 | uint16 | uint32 | uint64 | fixed point

Start of input frame indicator, specified as a Boolean scalar.

Data Types: Boolean

End of input frame indicator, specified as a Boolean scalar.

Data Types: Boolean

Valid input data indicator, specified as a Boolean scalar.

This is a control signal that indicates if the data on the dataIn port is valid.

Data Types: Boolean

Output

Decoded message data, returned as a scalar. This output data width is the same as the input data width.

Data Types: double | uint8 | uint16 | uint32 | uint64 | fixed point

Start of output frame indicator, returned as a Boolean scalar.

Data Types: Boolean

End of output frame indicator, returned as a Boolean scalar.

Data Types: Boolean

Valid output data indicator, returned as a Boolean scalar.

This is a control signal that indicates if the data on the dataOut port is valid.

Data Types: Boolean

Indications of corruption of the received data, returned as a Boolean scalar.

When this value is 1 (true) , the output

contains at least one error. When this value is 0

(false), the output contains zero errors.

If the number of errors in the input codeword is greater than (Codeword

length – Message length)/2, the

block outputs data without correcting the errors and sets the

errOut port to 1 (true)

to indicate that errors that cannot be corrected exist in the input codeword.

Data Types: Boolean

Number of corrected errors, returned as a nonnegative scalar.

The maximum number of errors an RS code can correct is equal to

(Codeword length – Message length)/2. If

the number of errors in the input codeword is greater than (Codeword

length – Message length)/2, the block outputs data

without correcting the errors and sets the numErrors port to

0 to indicate that none of those errors can be corrected.

Dependencies

To enable this port, select the Output number of corrected symbol errors parameter.

Data Types: uint8

Parameters

Specify the codeword length.

For more information on representing data for RS codes, see Integer Format (Reed-Solomon Only).

Specify the message length.

For more information on representing data for RS codes, see Integer Format (Reed-Solomon Only).

Specify the source of the primitive polynomial.

Select

Autoto specify the primitive polynomial based on the Codeword length parameter value. The degree of the primitive polynomial is calculated as M =ceil(log2(Codeword length).Select

Propertyto specify the primitive polynomial using the Primitive polynomial parameter.

Specify a binary row vector representing the primitive polynomial in descending order of powers.

For more information on how to specify a primitive polynomial, see Primitive Polynomials and Element Representations.

Dependencies

To enable this parameter, set the Source of primitive

polynomial parameter to Property.

Specify the source of the starting power for roots of the primitive polynomial.

Select

Propertyto enable the B value parameter.Select

Auto, to use the B value parameter default value of1.

The starting exponent of the roots.

Dependencies

To enable this parameter, set the Source of B, the starting power for

roots of the primitive polynomial parameter to

Property.

Select this parameter to enable the numErrors output port. This port outputs the number of corrected errors.

Algorithms

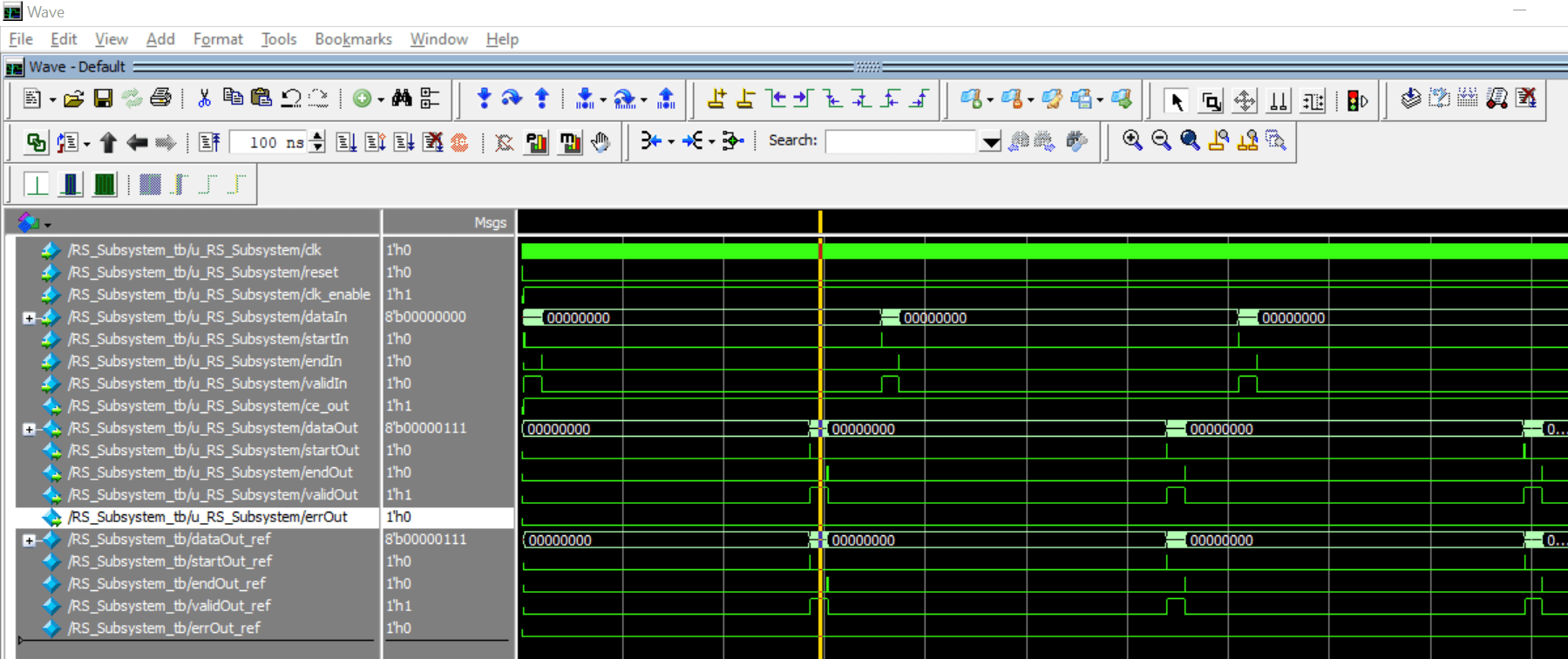

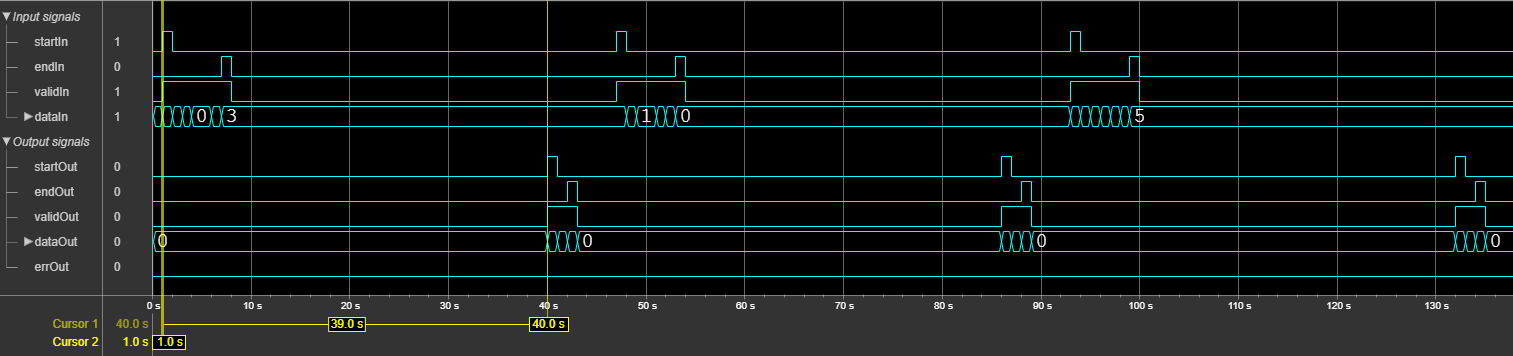

This figure shows a sample output of the Integer-Output RS Decoder HDL Optimized block with a default configuration.

Each input frame must contain symbols less than or equal to Codeword length. A shortened code is inferred when the number of valid data samples between startIn and endIn is less than Codeword length.

To get a proper output for two sequential input frames, the gap between the frames must be greater than the sum of the block latency and the Message length.

The generator polynomial is not specified explicitly. However, it is defined by the Codeword length, Message length, and the B value for the starting exponent of the roots.

The performance of the synthesized HDL code varies with the target and synthesis options. It also varies based on the input data type.

This table shows the resource and performance data synthesis results when you provide an

input data type of uint8, specify the Code length

parameter as 255, and Message length parameter as

223. The generated HDL is targeted to the AMD®

Zynq®- 7000 ZC706 evaluation board. The design

achieves a clock frequency of 58.09 MHz.

| Resource | Number Used |

|---|---|

| Slice LUTs | 8882 |

| Slice Registers | 5399 |

| DSPs | 0 |

| Block RAMs | 1 |

Extended Capabilities

Usage notes and limitations:

Not recommended for production code.

HDL Coder™ provides additional configuration options that affect HDL implementation and synthesized logic.

This block has one default HDL architecture.

| ConstrainedOutputPipeline | Number of registers to place at

the outputs by moving existing delays within your design. Distributed

pipelining does not redistribute these registers. The default is

|

| InputPipeline | Number of input pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| OutputPipeline | Number of output pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

You cannot generate HDL for this block inside a Resettable Synchronous Subsystem (HDL Coder).

Version History

Introduced in R2012bAdded a new section with resource and performance data synthesis results for the Integer-Output RS Decoder HDL Optimized block.

See Also

Blocks

Objects

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

选择网站

选择网站以获取翻译的可用内容,以及查看当地活动和优惠。根据您的位置,我们建议您选择:。

您也可以从以下列表中选择网站:

如何获得最佳网站性能

选择中国网站(中文或英文)以获得最佳网站性能。其他 MathWorks 国家/地区网站并未针对您所在位置的访问进行优化。

美洲

- América Latina (Español)

- Canada (English)

- United States (English)

欧洲

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)