HDL Code Generation and Deployment

DSP HDL Toolbox™ provides blocks and System objects that support HDL code generation. To generate HDL code from these designs, you must have HDL Coder. HDL Coder also enables you to generate scripts and test benches for use with third-party HDL simulators.

If you have an HDL Verifier license, you can use the FPGA-in-the-loop feature to prototype your HDL design on an FPGA board. HDL Verifier also enables you to cosimulate a Simulink® model with an HDL design running in a third-party simulator.

To design, prototype, and verify domain-specific practical applications on hardware, download hardware support packages such as SoC Blockset™ Support Package for AMD FPGA and SoC Devices and HDL Coder Support Package for AMD FPGA and SoC Devices.

Topics

- Prototype DSP HDL Algorithms on Hardware

Prototype DSP HDL Toolbox designs on FPGA and SoC boards using hardware support packages.

- Verify HDL Design Using SystemVerilog DPI Test Bench (HDL Coder)

This example shows how to use SystemVerilog DPI test bench for verification of HDL code where a large data set is required.

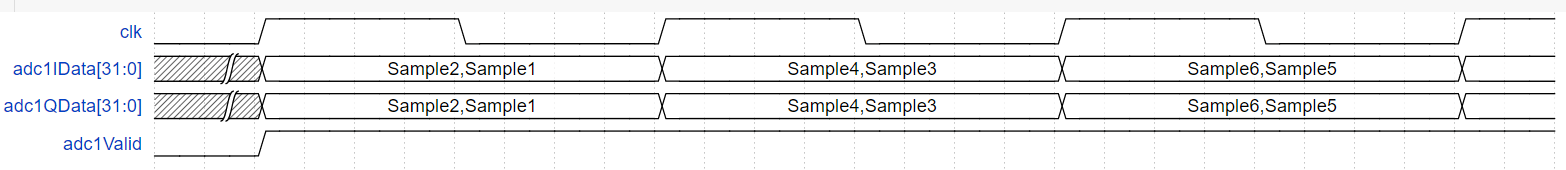

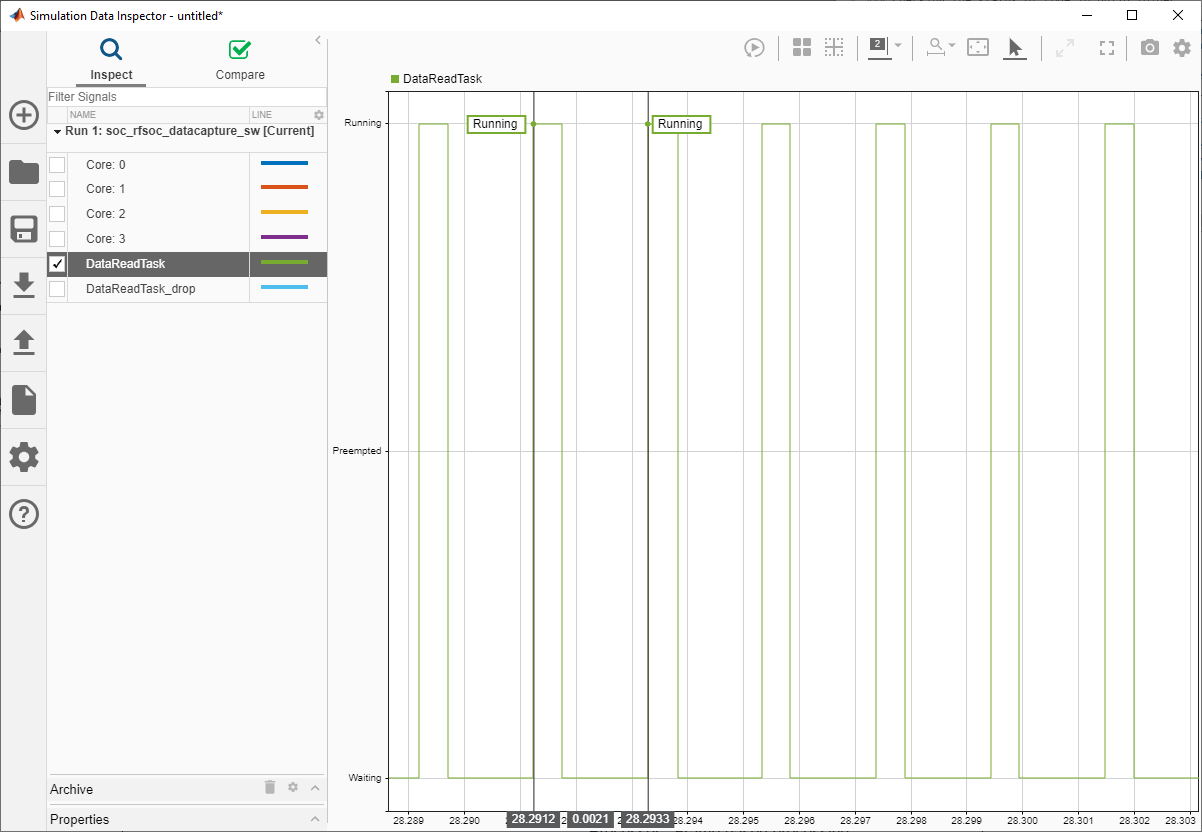

- Host Interface Script Data Capture from Polyphase Channelizer Algorithm on RFSoC device (HDL Coder)

This example shows how to use the HDL-optimized Channelizer block to process incoming analog-to-digital converter (ADC) samples and produce a spectrum that has 512 MHz of bandwidth.

- Configure Multi-Tile Synchronization on RFSoC Devices (HDL Coder)

This example shows how to use Multi-Tile Synchronization (MTS) for Zynq® UltraScale+™ RFSoC devices to ensure consistent timing and alignment between tiles and across devices.