Code Verification and Validation with PIL and External Mode

This example shows you how to use Embedded Coder Support Package for ARM Cortex-A Processors for code verification and validation using PIL and External Mode.

Introduction

This example shows you how to configure a Simulink model to run Processor-In-the-Loop (PIL) and external mode simulations. In a PIL simulation, the generated code runs a QEMU ARM Cortex-A9 emulator. The PIL simulation results get transferred to Simulink to verify the numerical equivalence of the simulation and the code generation results. The PIL verification process ensures that the behavior of the deployment code matches the design.

Simulink's External mode feature enables you to accelerate the process of parameter tuning by letting you change certain parameter values while the model is running on target hardware, without stopping the model. When you change parameter values from within Simulink, the modified parameter values are communicated to the target hardware immediately. The effects of the parameters tuning activity may be monitored by viewing algorithm signals on scopes or displays in Simulink.

With this approach:

You can verify code generated for subsystems

You must provide a test harness model to supply test vector or stimulus inputs

You must swap your original subsystem with an automatically generated PIL block; you should be careful to avoid saving your model in this state as you would lose your original subsystem.

Requirements

Verify Generated Code using PIL Block

This section show you how to automatically generate a PIL block that can be used for verification. The objective is to create a PIL block out of the Controller subsystem running on the QEMU emulator.

1. Open the arm_cortex_a_pil_block model.

2. Enable PIL feature in the arm_cortex_a_pil_block model. On the Hardware tab, click Hardware Settings. In the Search bar, enter CreateSILPILBlock. In the Create block parameter, set PIL. Click OK.

3. Create a PIL block for the Controller subsystem. Left-click on the Controller subsystem and click C/C++ > Deploy this Subsystem to Hardware. In the Build code for Subsystem: Controller window, click the Build button to create a PIL version of the Controller subsystem block in a new model.

4. Copy PIL block into the empty space in the arm_cortex_a_pil_block model.

5. On the Simulation tab, click Run to start the PIL simulation.

6. Once you start simulating the model, the PIL executable starts running on the QEMU emulator. You can switch between the original and PIL block subsystems by double clicking on the Manual Switch block. Double click on the Numerical Differences block to see the difference between the simulated Controller subsystem and the PIL block running on the QEMU emulator.

Verify Generated Code using PIL Simulation for Model Blocks

This task shows you how to verify the automatically generated code for a referenced model by running a PIL simulation. With this approach:

You can verify code generated for referenced models

You must provide a test harness model to provide test vector or stimulus inputs

You can easily switch a Model block between normal and PIL simulation mode

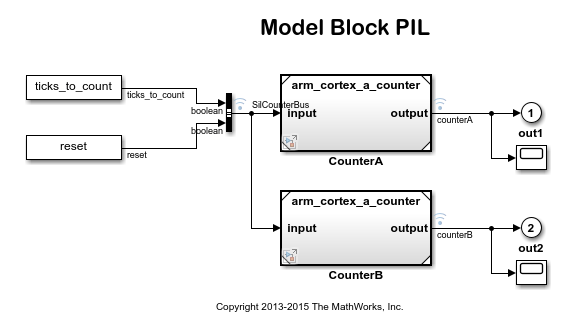

1. Open arm_cortex_a_model_pil_block model.

The model contains two Model blocks that both point to the same referenced model. You will configure one of the Model blocks to run in PIL simulation mode and the other in normal mode.

2. On the Apps tab, under Code Verification, Validation and Test, click SIL/PIL Manager.

3. On the SIL/PIL tab, set System Under Test to Model blocks in SIL/PIL mode.

4. Configure and run CounterA block in PIL simulation mode. Open the CounterA block mask by right-clicking on the block and selecting Block Parameters (ModelReference). In the Function Block Parameters: CounterA window, set Simulation mode to Processor-in-the-loop (PIL). Click OK.

5. On the SIL/PIL tab, click Run Verification to start the PIL simulation.

6. When model starts running, Scope1 displays the PIL simulation output running on the Xilinx Zynq hardware. Scope2 shows the normal mode simulation output.

Verify Generated Code Using PIL Simulation for Top Models

This example shows how you can verify the automatically generated code for a top model by running a PIL simulation. With this approach:

You can verify code generated for a top model.

You can easily switch the entire model between normal and PIL simulation mode.

You must configure the model to load test vectors or stimulus inputs from the MATLAB workspace.

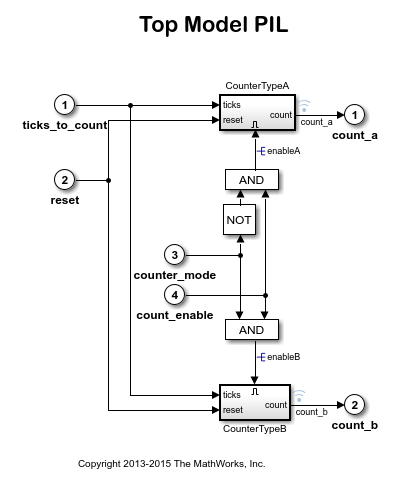

1. Open the arm_cortex_a_top_model_pil model.

2. On the Apps tab, under Code Verification, Validation and Test, click SIL/PIL Manager.

3. On the SIL/PIL tab, set SIL/PIL mode to Processor-in-the-loop (PIL).

4. On the SIL/PIL tab, click Run Verification to run the PIL simulation.

5. When the PIL simulation completes, a logsOut variable gets added to the base workspace containing the PIL simulation results. You can access the logged data for signals count_a and count_b using the following commands:

count_a = get(logsOut,'count_a'); count_a.Values.Data count_b = get(logsOut,'count_b'); count_b.Values.Data

External Mode

This task shows you how to run a Simulink model in external mode. When prototyping and developing an algorithm, monitoring and tune the algorithm while it executes on an embedded processor can be useful. External mode in Simulink enables this capability.

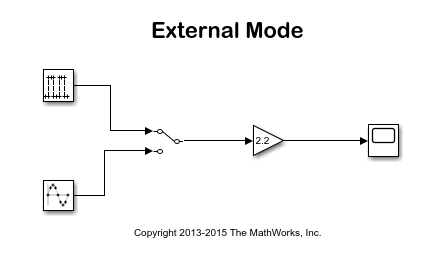

1. Open the arm_cortex_a_external_mode model.

2. On the Hardware tab, click Monitor & Tune to start the external mode simulation. You can stop the simulation at any time by clicking the Monitor & Tune again.

3. After the model builds, deploys, and starts running on the QEMU emulator, you can double-click the Manual Switch block to change the input source. Open the Gain block to change the signal gain. Finally, double click on the Scope block to view the External mode simulation results.

For additional external mode simulation settings, you can open the External Mode Control Panel. On the Hardware tab, click Control Panel to open the External Model Control Panel.