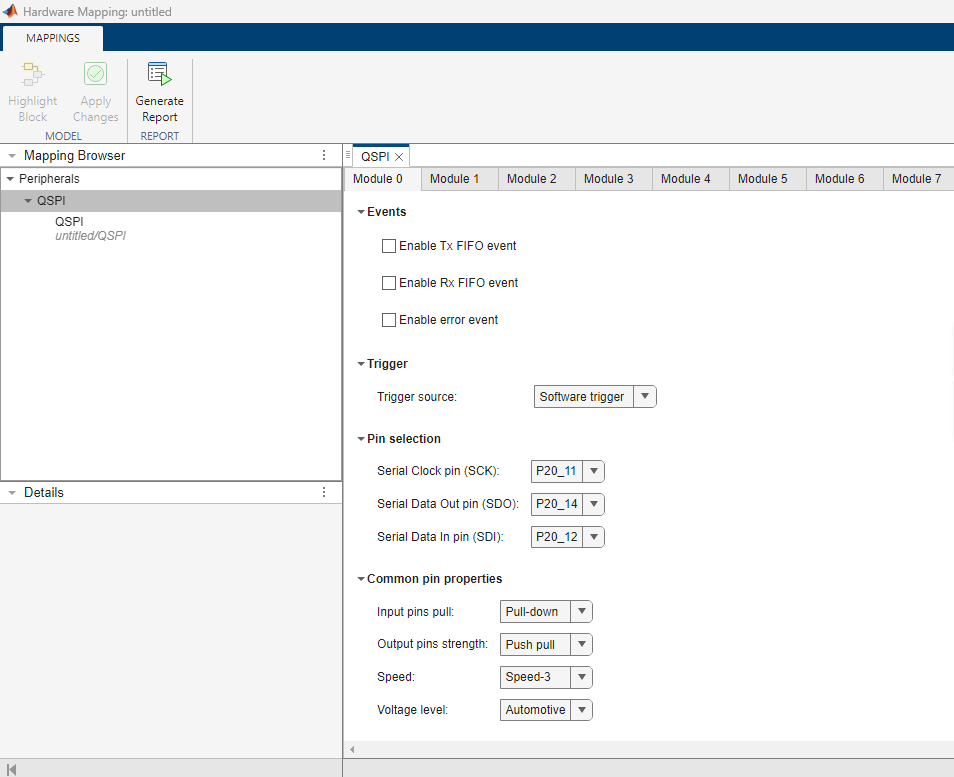

QSPI Peripheral Configuration

Map QSPI peripherals in the Infineon AURIX model to peripheral registers in the MCU

Since R2022b

Description

Add-On Required: This feature requires the Embedded Coder Support Package for Infineon AURIX TC4x Microcontrollers add-on.

View and edit the map of peripherals in the Infineon® AURIX™ model to the hardware peripherals.

Using the Peripheral Configuration tool, you can:

View and edit configuration parameters for QSPI peripheral block.

Configure the global parameters. To set the group peripheral, select peripheral in Browser > Peripherals >

QSPI. For more, see Map Tasks and Peripherals Using Hardware Mapping.Check for any conflicts between peripherals.

Open the QSPI Peripheral Configuration

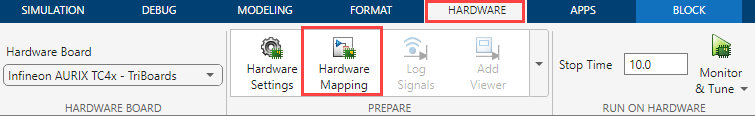

In the Simulink toolstrip, go to Hardware tab and click Hardware Mapping.

Examples

Parameters

Version History

Introduced in R2022b