Software Architecture of Generated Motor Control Models

This topic explains the software architecture of the models generated by the Generate Motor Control Models for Selected Algorithm and Hardware example. The example generates a host and a target Simulink® model.

The host model is a user interface to the controller hardware board. You can run the host model on the host computer. The prerequisite to use the host model is to deploy the target model to the controller hardware board. The host model uses serial communication to command the target Simulink model and run the motor.

The target model implements the control algorithm, device drivers for motor control and a plant model for simulation. The plant includes implementation for target inverter hardware and motor equations. In the absence of a real motor and hardware, you can use this plant along with the microcontroller algorithm to simulate the motor control application using a speed reference.

When you generate code and deploy the target model, the system generates embedded C code for the microcontroller algorithm that includes driver and driver abstraction implementation along with application and application abstraction implementation and deploys it to the target microcontroller unit.

The Generate Motor Control Models for Selected Algorithm and Hardware example supports the following three microcontroller units:

STM32G4xx family processor based boards

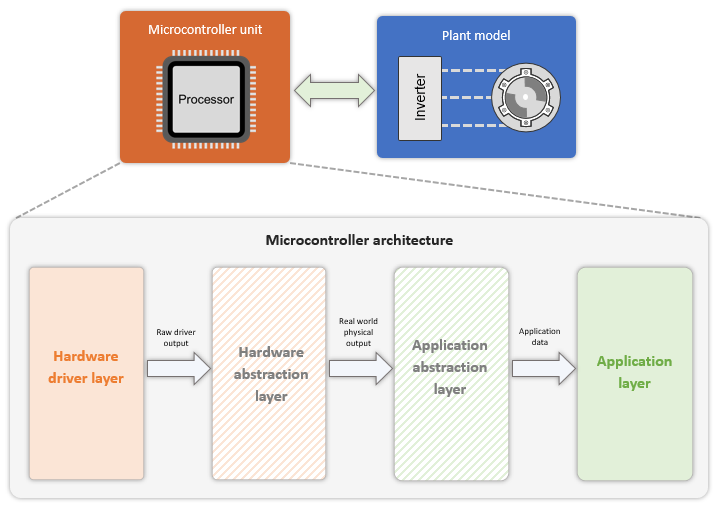

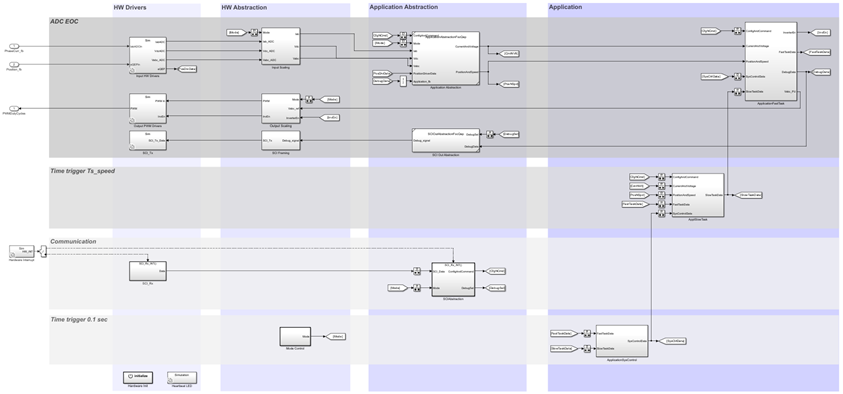

This image shows the architecture of the motor control algorithm.

The following sections briefly describe the algorithm architecture.

Hardware Drivers

The hardware drivers (or device drivers) include the driver blocks and other interfaces for hardware modules such as the analog to digital converter (ADC), sensor decoders, pulse-width modulation (PWM) switching module, GPIO and serial communication units among others. This also includes hardware initialization and interrupt scheduling routines, which ensure that ADC and PWM are always synchronized.

It primarily accepts motor phase currents and rotor position as inputs and outputs the PWM duty cycles that operate the inverter switches to control the motor.

It also generates raw driver data (including ADC current counts as well as voltage and position sense information) that is further processed by the hardware abstraction (or driver abstraction).

For more information about designing and configuring this layer, see Add Hardware Drivers to Simulation Model and Deploy to Target Hardware.

Hardware Abstraction

The hardware abstraction (or driver abstraction) acts as an interface between the drivers and the controller application. It accepts raw data from the drivers and converts and scales it into real-world SI unit current and voltage signals.

In addition, this module receives the reference voltage signals from the controller application and scales them to the range required by the PWM drivers.

Application Abstraction

The application abstraction acts as an interface between the drivers and the application. It accepts the real-world current and voltage signals from the hardware drivers for processing and then groups and formats them into a data format compatible with the motor control algorithm.

In addition, the application abstraction layer also performs functions critical to the motor control system such as real-time computation of motor position and speed.

Application

The application is the top-most decision-making unit of the entire microcontroller algorithm. Based on the controller that you select, this module includes either an open-loop (V/F or scaler) control or a closed-loop (vector) algorithm like FOC. The module accepts motor phase currents and rotor position information from the application abstraction and uses reference speed information to derive reference voltages. These voltages are used by the hardware abstraction (or driver abstraction) for generating PWM voltages.

The Generate Motor Control Models for Selected Algorithm and Hardware example uses the hardware drivers and hardware abstraction layers as a base according to the selected hardware. Afterwards, based on the controller selection, the example updates the subsystem references for the application abstraction and application modules to build the entire target model. The example also updates the subsystem references in the host model for user inputs and outputs based on the selected control algorithm.