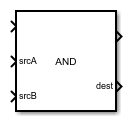

AND

Bitwise AND

Libraries:

Description

The AND block implements the AND ladder logic

instruction. When the rung conditions are true, the block performs bitwise AND operation on

the values at source A with the values at source B. The result of this operation is available

at the destination port (dest).

Ports

Input

Output

Version History

Introduced in R2019a