支持 SPI 通信

SPI(即串行外设接口)是一种高速设备之间的短距离同步、全双工串行通信协议。SPI 协议支持单个控制器带一个或多个外围设备。该控制器可以与总线上的任何外围设备通信,但每个外围设备只能与控制器通信。

支持包库中的 SPI Controller Transfer 模块支持与其他 SPI 设备的通信。仅当您将硬件用作控制器设备时,才能使用此模块。

使用 SPI,您可以:

将各种传感器连接到板以测量温度、压力等不同量。

将各种扩展板连接到板以增强功能,例如 Wi-Fi® 扩展板。

访问 SD 卡以存储数据或扩展可用内存。

您可以在配置参数 > 硬件实现 > SPI 属性部分设置 SPI 属性,例如 SPI 时钟输出频率(以 MHz 为单位)、SPI 模式和位序。

SPI 线

SPI 使用一个四线串行总线进行通信:SDI、SDO、SCK 和 CS。SDI、SDO 和 SCK 线通用于所有设备。SS 线特定于每个外围设备。

SDI(串行数据输入)- 此线是外围设备向 SPI 控制器发送数据的线。

SDO(串行数据输出)- 此线是控制器向 SPI 外围设备发送数据的线。

SCK(串行时钟)- 控制器生成用于同步数据传输的时钟脉冲。

CS(片选)- 此线特定于设备。这是每个设备上的引脚,SPI 控制器可以使用它来启用和禁用设备。此信号是“低电平有效”信号,这意味着当设备的 SS 引脚设置为低电平时此设备成为外设。

在如下所示的所有板上,输入电路串行编程 (ICSP) 排针接口上的 SPI 线都是一致的。

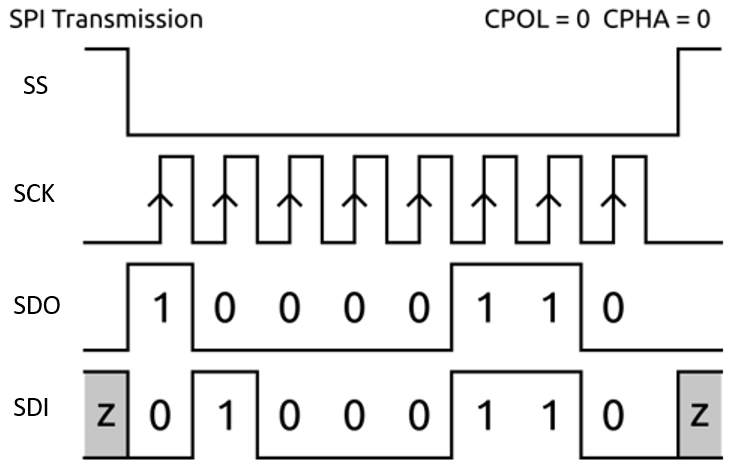

数据传输

SPI 控制器会设置受控制器要与之通信的 SPI 外设支持的时钟频率。

控制器通过将外设的 SS 引脚设置为低电平 (0) 来选择外围设备。控制器一次只能选择一个外设。

由于每个 SPI 传输都是全双工传输,因此控制器会在 SDO 线上发送一个位,外围设备会读取该位。外围设备也会在 SDI 线上发送一个位,控制器会读取该位。

当控制器进行数据传输时,外设无法选择不发送数据。但是,当通信是单向时,外围设备会发送虚拟字节(通常全为 1 或全为 0)。同样,当控制器从外设读取数据时,该外设知道忽略控制器发送的数据。

在传输完成后,控制器停止切换 SCK,并且通常会拉高 SS 以取消选择外围设备。

在数据传输期间,SPI 总线上未被控制器选择的其他外围设备会忽略 SCK 和 SDO 信号,并且不驱动 SDI。

SPI 传输模式

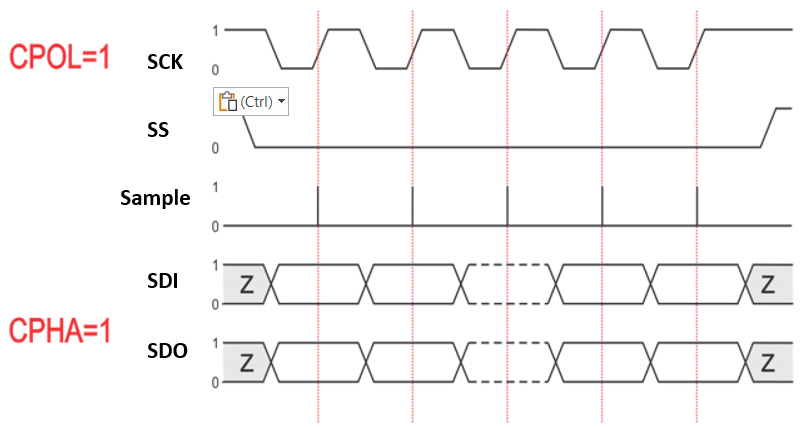

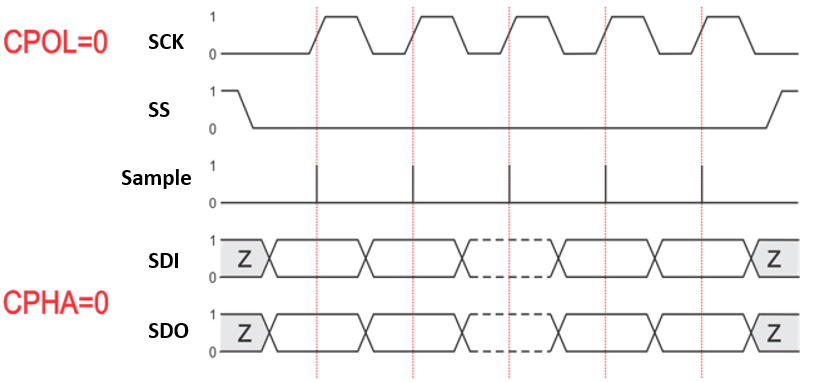

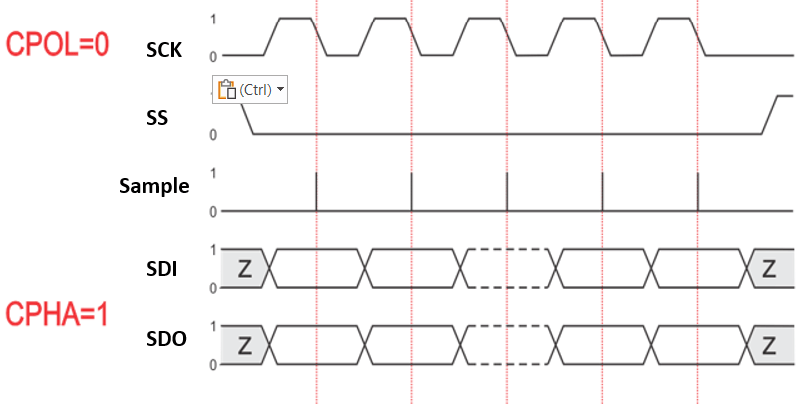

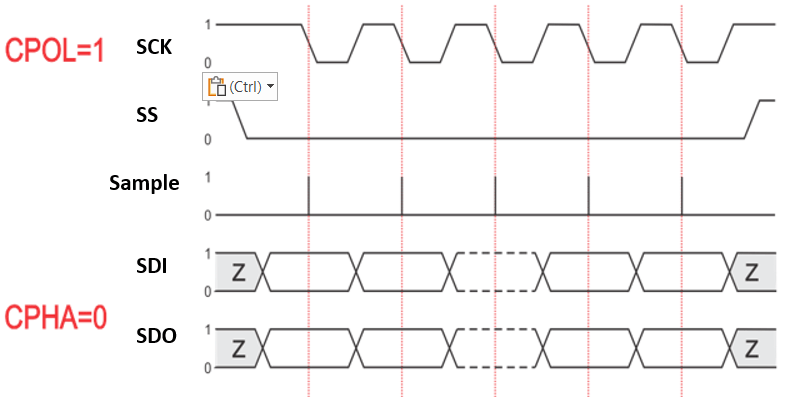

SPI 控制器会设置时钟极性和时钟相位。

时钟极性 (CPOL) - 是在总线闲置时 SCK 信号的默认值 (HIGH/LOW)。

CPOL = 0 表示在总线闲置时 SCK 的默认值为 LOW。CPOL = 1 表示在总线闲置时 SCK 的默认值为 HIGH。

时钟相位 (CPHA) - 指示是在 SCK 的 LEADING(第一个)沿还是 TRAILING(第二个)沿对时钟数据进行采样。

CPHA = 0 表示在 SCK 的 LEADING 沿采样,CPHA = 1 表示在 SCK 的 TRAILING 沿采样,无论时钟沿是 RISING 还是 FALLING。

极性和相位的组合称为 SPI 模式。SPI 模式 0-3 如下表所示。

| 模式 | 时钟极性 (CPOL) | 时钟相位 (CPHA) |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 2 | 1 | 0 |

| 3 | 1 | 1 |

模式 0

模式 1

模式 2

模式 3