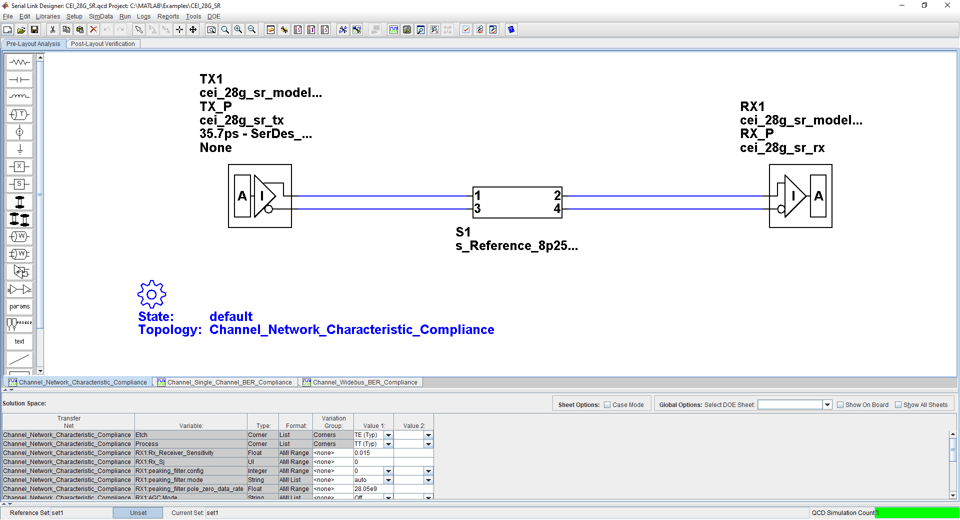

CEI 28G-SR Compliance Kit

Characterize and validate the performance of a CEI 28G-SR channel design.

CEI 28G-SR is a common electrical interface (CEI) implementation agreement (IA) that supports 28 Gb/s over "Short Reach" (SR) chip-to-chip applications. The CEI-28G-SR Clause is part of the Common Electrical I/O 3.0 Implementation Agreement.

This kit is designed for analysis of a host board and QSFP+ 100G module. The total channel length is approximately 8.25 inches. It consists of a host board connected with a mated connector which represents the interconnect between the transmitting and receiving 28.05 Gb/s data across the channel. The kit has three sheets; one for single channel BER compliance testing, one for multi-channel FEXT/NEXT crosstalk to measure BER compliance and a sheet for simulating network characteristics for compliance.

This kit enables you to insert a channel design and characterize and validate its performance using the specification masks to determine if the channel has a high confidence of success. If the channel does not meet the compliance masks or BER estimates, further investigation or redesign, along with simulation, will need to be performed to determine possible changes to meet compliance.

Open CEI 28G-SR Kit

Open the CEI 28G-SR kit in the Serial Link Designer app using the openSignalIntegrityKit function.

openSignalIntegrityKit("CEI_28G_SR");

Kit Overview

Project Name: CEI_28G_SR

Interface Name: CEI_28G_SR

Operating Frequency: 28.05 Gbps (UI = 35.75ps)

The CEI 28G-SR kit defines one schematic set.

Default – Schematic sheets focused on channel characterization and BER compliance

For more information about the CEI 28G-SR channel compliance schematics, transfer net properties, and compliance rules, refer to the document CEI_28G_SR.pdf that is attached to this example as a supporting file.