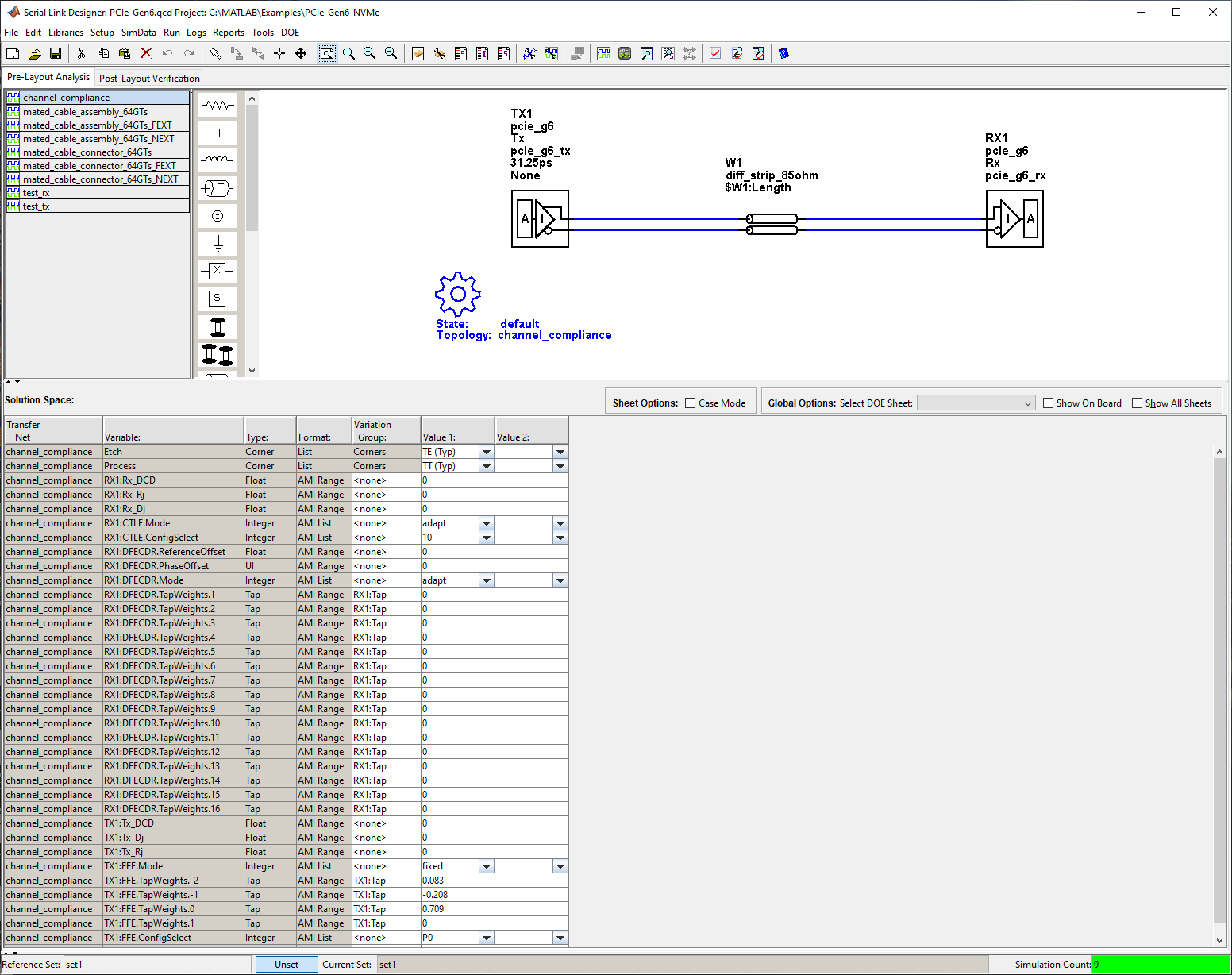

PCIe-6 Compliance Kit

Test the compliance of simulation models and topologies based on the PCI Express 6.0 Base Specification (PCIe-Gen6) and the Internal Cable Specification for PCI Express 5.0 and 6.0.

This PCIe 6.0 compliance signal integrity kit includes transfer nets, topologies, generic IBIS-AMI buffer models and compliance rules for a PCIe 6.0 high-speed SerDes interface. This includes PCIe 6.0 technology IBIS-AMI models for the SerDes transmitter and receiver, compliance masks and transfer nets preconfigured for TX and RX characterization that are customizable for a target physical layer design.

This kit enables you to insert a channel design and characterize and validate its performance using the specification masks to determine figures of merit with regards to signal integrity performance. If the channel does not meet the compliance masks or BER estimates, further investigation or redesign, along with simulation, may need to be performed to determine possible changes to meet compliance.

Open PCIe-6 Kit

Open the PCIe-Gen6 kit in the Serial Link Designer app using the openSignalIntegrityKit helper function.

openSignalIntegrityKit("PCIe_Gen6_NVMe");

Kit Overview

Project Name: PCIe_Gen6_NVMe

Interface Name: PCIe_Gen6

Target Operating Throughput: 64.0 GT/s with PAM4 Modulation

For more information about the PCIe-Gen6 compliance kit for Serial Link Designer provided with Signal Integrity Toolbox, refer to the document PCIe_Gen6.pdf that is attached to this example as a supporting file.

Copyright 2023, The MathWorks, Inc.