UCIe 1.0 Compliance Kit

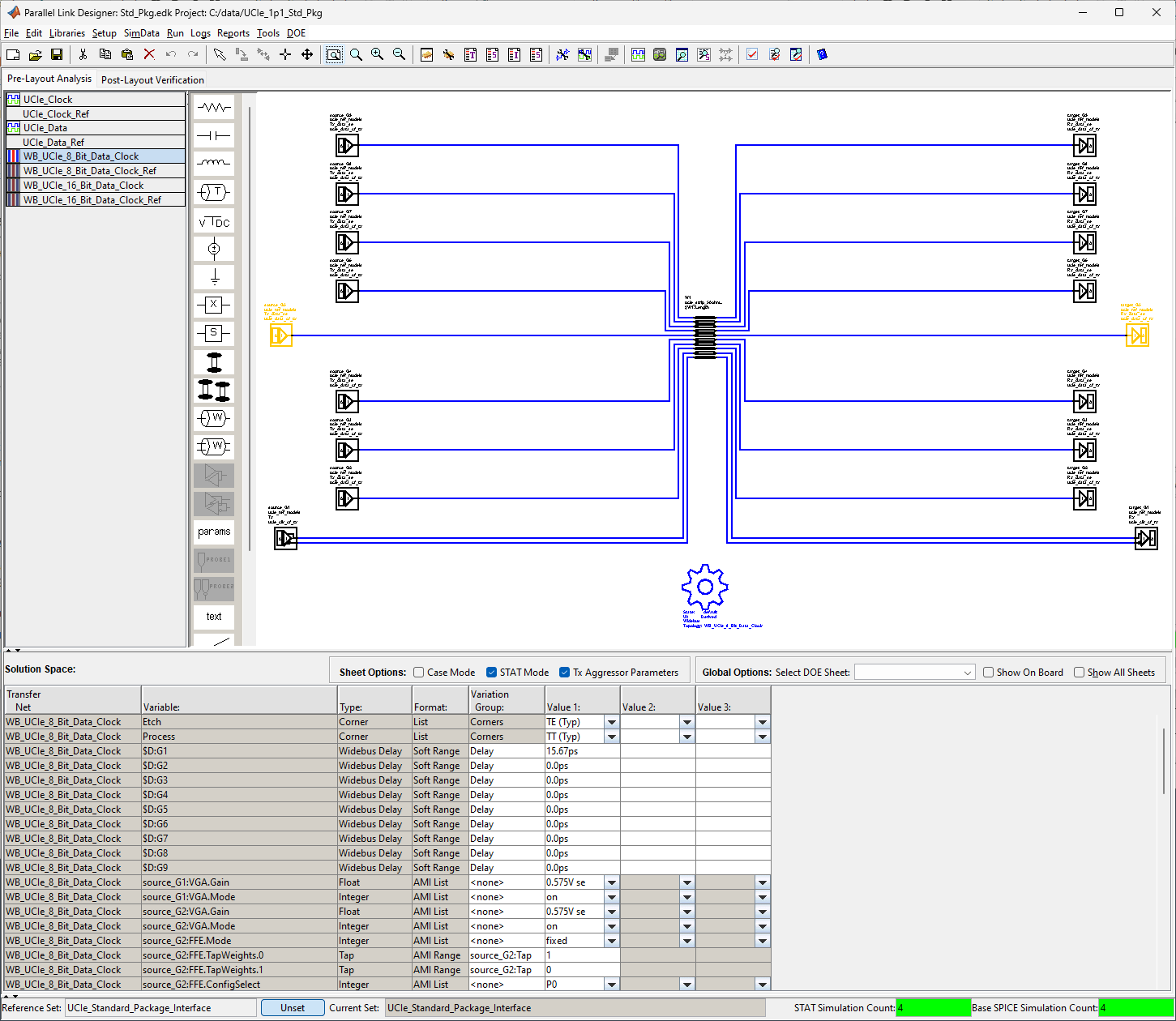

This example shows you how to implement a Universal Chiplet Interconnect Express (UCIe) Version 1.0 (Specification Revision 1.1) interface for pre-layout analysis or post-layout verification using Parallel Link Designer from Signal Integrity Toolbox™.

This UCIe signal integrity compliance kit includes transfer nets, mask compliance checks, waveform processing levels and generic IBIS-AMI models for a UCIe interface. This includes generic buffer models for the UCIe transmitter and receiver. You can modify the kit to match your specific design implementation and perform complete pre-layout solution space analysis and/or full post-layout verification for waveform quality and compliance margins.

Open Compliance Kit

You can open the compliance kit in the Parallel Link Designer app using the openSignalIntegrityKit function.

openSignalIntegrityKit("UCIe_1p1_Std_Pkg");

Kit Overview

For more information about this UCIe signal integrity compliance kit, including block diagrams, system configurations, transfer nets and libraries, refer to the document UCIe_v1p0_r1p1.pdf that is attached to this example as a supporting file.

Note: This kit also supports UCIe version 2.0.

References

[1] UCIe Version 1.0, Specification Revision 1.1: https://www.uciexpress.org