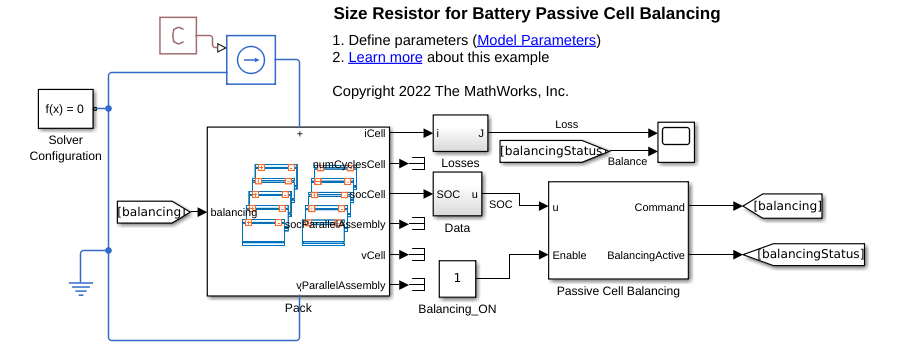

用于电池无源电芯平衡的尺寸电阻器

此示例说明了如何为锂离子电池包实现无源电芯平衡。电池模组中电池电芯之间的差异会导致电池电芯的荷电状态 (SOC) 和电压失衡。在此例中,当电池包处于空闲状态且电池电芯 SOC 差值大于预定义值时,平衡算法启动。被动平衡分流电阻器的选型基于功率损耗和平衡时间的考虑。

构建电池包

要构建此示例中使用的电池包,请按照 构建带电芯平衡电路的电池包模型 示例中的步骤操作,并在工作目录中生成 batt_PackWithCellBalancingLib SLX 文件。该 SLX 文件包含用于电芯平衡应用的电池包模型。该电池包由两个模组组件组成。每个模组组件都包括两个模组。每个电池模组有 16 个电芯。打开 batt_PackWithCellBalancingLib SLX 文件,将 Pack 子系统拖放到模型中,并将其连接到 Passive Cell Balancing 模块。Passive Cell Balancing 模块使用电芯 SOC 作为平衡参数。

定义参数

初始化电池参数。

run("batt_PackWithCellBalancing_param");在此示例中,平衡阈值等于 SOC 的 0.1%。

threshold_balancing_SOC = 1e-3;

对于 ModuleAssembly1 对象中的两个模组,定义所有 16 个初始电芯 SOC。

ModuleAssembly1.Module1.socCell =... [0.69;0.69;0.69;0.69;... 0.715;0.715;0.715;0.715;... 0.7;0.7;0.7;0.7;... 0.7;0.7;0.7;0.7]; ModuleAssembly1.Module2.socCell =... ModuleAssembly1.Module1.socCell;

对 ModuleAssembly2 对象中的两个模组执行相同的操作。

ModuleAssembly2.Module1.socCell =... [0.69;0.69;0.69;0.69;... 0.715;0.715;0.715;0.715;... 0.7;0.7;0.7;0.7;... 0.7;0.7;0.7;0.7]; ModuleAssembly2.Module2.socCell =... ModuleAssembly2.Module1.socCell;

指定要评估的分流电阻器选项。

balancingResistor_options = [2 3 4 5 6]; % all Resistances in Ohm运行仿真

对 balancingResistor_options 变量中指定的所有平衡电阻器选项进行模型仿真。在 MATLAB® 命令行窗口中,运行 batt_PackWithCellBalancingSimulate 文件。

run('batt_PackWithCellBalancingSimulate')

该文件对所有平衡电阻器选项进行仿真,并将输出结果存储在 batt_PackWithCellBalancingResults MAT 文件中。

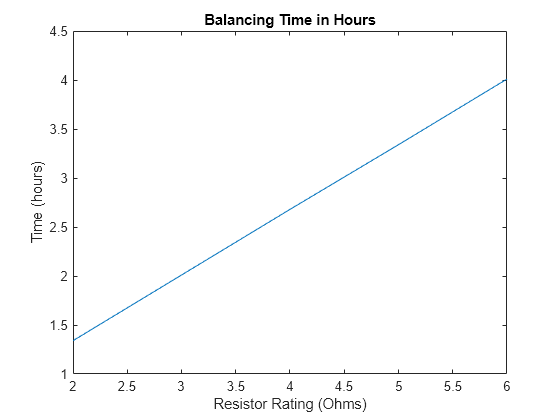

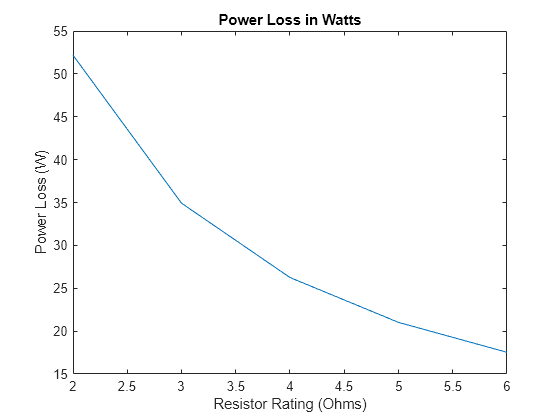

分析结果

加载 batt_PackWithCellBalancingResults MAT 文件,在 MATLAB 命令行窗口中输入:

run("batt_PackWithCellBalancingPlot")

第一个图显示了每个电阻器额定值的平衡时间,单位为小时。对于 4 欧姆的电池包电阻器,电池 SOC 在大约 2.5 小时后达到平衡。

第二个图显示了每个电阻器额定值的功率损耗(以瓦特为单位)。一个 4 欧姆的电阻器会产生大约 25 瓦的功率损耗。

4 欧姆电阻器是最终硬件设计的良好折中方案。