隔离引用模型进行功能测试

要对引用模型进行功能测试,您可以创建一个引用模型的切片,该模型被视为开环模型。您可以将简化的开环引用模型与通过仿真闭环系统生成的输入隔离开来。

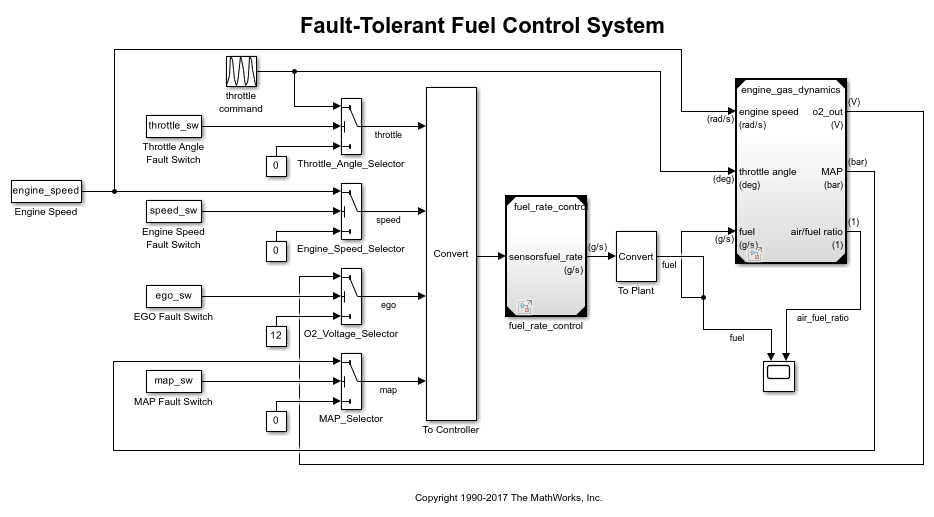

此示例说明如何对容错燃油控制系统的引用模型控制器进行切片,以便进行功能测试。要创建一个简化的开环引用模型用于调试和细化,需要生成引用控制器的切片。

步骤 1:打开模型

容错燃油控制系统模型包含一个引用模型控制器 fuel_rate_control。

open_system('sldvSlicerdemo_fuelsys');

步骤 2:对引用模型进行切片

要分析 fuel_rate_control 引用模型,请对其进行切片以创建一个独立的开环模型。要打开模型切片管理器,请选择 App > 模型验证、确认和测试 > 模型切片器,或右键点击 fuel_rate_control 模型并选择模型切片器 > 对组件进行切片。打开模型切片管理器时,模型切片器会编译模型。然后配置模型切片属性。

注意:sldvSlicerdemo_fuelsys 模型的仿真模式是 Accelerator 模式。对引用模型进行切片时,软件会将仿真模式配置为 Normal 模式,并在退出模型切片器时将其设置回原始仿真模式。

步骤 3:选择起点

打开 fuel_rate_control 模型,右键点击 fuel-rate 端口,并选择模型切片器 > 添加为起点。模型切片器会突出显示影响 fuel_rate 的上游构造。

步骤 4:生成切片

a.在“模型切片管理器”对话框中,选择仿真时间窗。

b.点击运行仿真。

c.对于停止时间,输入 20。点击确定。

d.点击生成切片。软件通过使用闭环 sldvSlicerdemo_fuelsys 模型的输入对切片的引用模型进行仿真。

对于切片模型,在“信号编辑器”窗口中,将显示一个测试用例,该测试用例表示在仿真时间 0-20 秒内输入到引用模型的信号。