Time-Domain Model Verification

This example shows how to perform time-domain model verification using Simulink® Design Optimization™ Model Verification blocks. During time-domain verification, the software monitors a signal to check if it meets time-domain characteristics such as step response characteristics and upper and lower amplitudes, or tracks a reference signal.

You can also use blocks from Simulink and Simulink Control Design™ Model Verification libraries to design complex assertion logic for time-domain and frequency-domain verification, and signal monitoring.

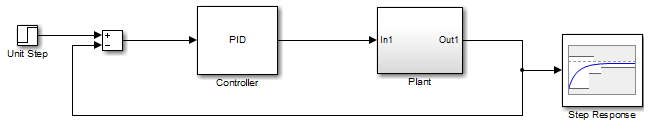

For example, consider the following Simulink model.

The model includes a Step Response block which is a Check Step Response Characteristics block from the Simulink Design Optimization Model Verification library. The block has step response bounds.

When you simulate such a model and the block asserts multiple times during simulation that the signal to which the block is connected violates the specified bounds, assertion warnings appear in the MATLAB® command window.

You can optimize model parameters to satisfy the bounds and eliminate assertion warnings. See Design Optimization to Meet Step Response Requirements (GUI).