本页面提供的是上一版软件的文档。当前版本中已删除对应的英文页面。

模块简化

模块简化可在模型仿真期间以及在生成的代码中提高执行速度。启用模块简化后,某些模块组可以合并为单个模块,甚至可以完全删除。

使用 Simulink® Design Verifier™ 时,模块简化会自动进行,并且未使用的代码路径中的模块将从模型中消除。Simulink Design Verifier 结果不包含已被简化模块的测试目标。

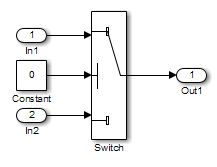

假设有以下模型中的 Switch 模块。

对于此 Switch 模块,控制输入始终为 0。如果首个输入传递条件模块参数为 u2 ~= 0,则 Switch 模块始终会将第三个输入传递到输出端口。当您分析此模型时,Simulink Design Verifier 会从模型中删除 Switch 模块,并且不会报告 Switch 模块的任何测试目标。

有关模块简化的详细信息,请参阅Block reduction参数的描述。