使用观察者隔离验证逻辑

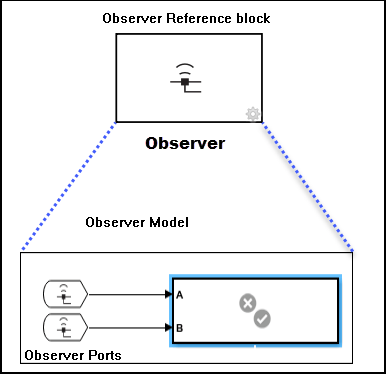

观察者使您能够跟踪系统模型的变化行为,而无需改变其设计或影响系统结果的准确性。观察者使用两种类型的模块:Observer Reference 方块和 Observer Port 模块。Observer Reference 模块引用称为 Observer 模型的独立模型。您可以分析以与设计模型不同的基本速率运行的 Observer 模型 (自 R2024b 起)。

您可以使用 Observer Reference 模块隔离模型中的验证逻辑。当您想将验证逻辑与设计模型分开时,请使用 Observer Reference 模块。当您使用 Observer Reference (Simulink Test) 时,您可以对 Observer 模型进行更改,而无需更改设计模型。使用 Observer Reference 模块可以帮助您在模型设计早期或跨多个模型设计指定属性或需求。Observer Reference 模块还允许您:

模型设计需求作为属性,并使用 Simulink® Design Verifier™ 来证明它们。

根据捕获的输出建立基线结果并检测模型回归。

使用自定义测试目标生成功能设计需求的测试用例。

双击 Observer Reference 模块以打开 Observer 模型。Observer Reference 模块只能位于系统模型的顶层,并且没有输入端口。有关详细信息,请参阅 使用 Observer 以无线方式访问模型数据 (Simulink Test)。

用 Observer Reference 模块替换验证子系统

在编写自定义验证目标时,可以使用 Observer Reference 模块代替 Verification Subsystem 模块。Observer Reference 模块引用一个单独的验证模型,称为 Observer 模型,您可以使用该模型来验证您的系统模型。将 Verification Subsystem 模块转换为 Observer Reference 模块可以使系统模型更加清晰。要将 Verification Subsystem 模块转换为 Observer Reference 模块,请右键点击验证子系统并选择观察者 > 将选定模块移动到 Observer > 新建 Observer。此操作无法撤消。此操作会将 Observer Reference 模块添加到您的系统模型并打开 Observer 模型。您必须将 Observer 模型保存在 MATLAB® 路径下的可写文件夹中。

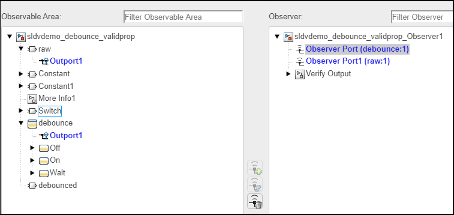

考虑模型 sldvdemo_debounce_validprop 包含 Verification Subsystem 模块 Verify Output 的情况。

通过将子系统转换为 Observer Reference 模块,您可以删除将子系统连接到系统模型的信号,同时保留测试系统完整性的能力。

两个信号 debounce 和 raw 自动映射到 Observer 模型中的两个 Observer Port 模块 sldvdemo_debounce_validprop_Observer1。

您可以验证 sldvdemo_debounce_validprop 的属性,而无需对设计模型进行任何更改。

关于 Observer Reference 模块的报告

如果您的模型包含 Observer Reference 模块,则 Simulink Design Verifier 分析报告将显示 Observer 模型子部分中 Observer Reference 模块的属性证明、测试用例生成和设计错误信息以及设计模型子部分中的设计模型信息。有关详细信息,请参阅 查看结果。

限制

Simulink Design Verifier 不支持:

包含 Model 模块的 Observer 模型

Observer 模型观察恒定信号

将模块替换规则应用于 Observer 模型

调整 Observer 模型中的参数

针对包含 Observer Reference 模块的模型,对 Embedded Coder® 生成的代码进行测试生成

对应的 Observer Reference 模块位于模型引用层次结构中的观察者模型

使用可变步长求解器设置执行分析的 Observer 模型

注意

如果 Observer 模型包含此列表中的任何限制,软件将在分析过程中忽略相应的 Observer Reference 模块。

当您执行以下操作时,Simulink Design Verifier 分析将返回错误:

分析独立的 Observer 模型

对 Observer Reference 模块执行子系统提取

另请参阅

Observer Port (Simulink Test) | Observer Reference (Simulink Test) | 使用 Observer Reference 模块进行属性证明分析 | 使用 Observer Reference 模块生成测试用例

外部网站

- 使用 Observer 以无线方式访问模型数据 (Simulink Test)