WLAN Receiver Using Analog Devices AD9361/AD9364

This example shows how to deploy a WLAN HDL receiver system to retrieve the signal and data field information from a WLAN signal for the 20 MHz channel bandwidth.

Overview

This example uses the WLAN receiver algorithm from the HDL Implementation of WLAN Receiver (Wireless HDL Toolbox) example to deploy a hardware-software (HW/SW) co-design implementation targeted on the Analog Devices AD9361/AD9364 radio platform. The example supports BPSK and QPSK modulation and coding schemes (MCS) for non-high-throughput (non-HT), high-throughput (HT), and very-high-throughput (VHT) frame formats. Additionally, the example shows you how to integrate a Simulink® model with the Zynq® hardware architecture.

For a list of supported Zynq radio hardware platforms, see Hardware Support.

To work with the HW/SW co-design workflow, you must install and configure additional support packages and third-party tools. For more information, see Installation for Hardware-Software Co-Design.

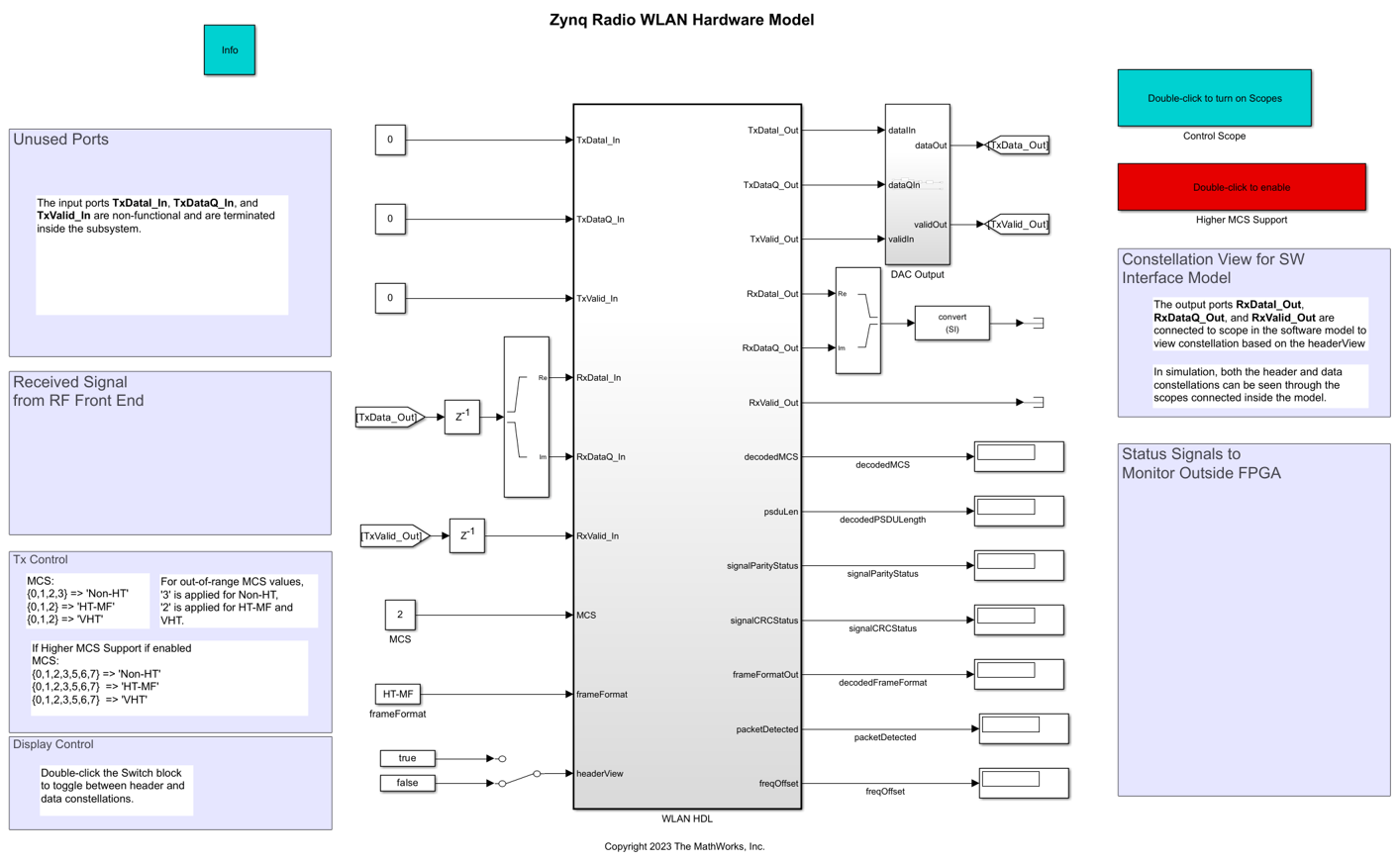

This figure shows a conceptual overview of the example.

The WLAN HDL Transmitter block accepts MCS and frame format control signals, and transmits WLAN packets by using lookup tables (LUTs). The LUT data for this example was generated by using the WLAN Toolbox™ and the 20 MHz channel bandwidth option. The WLAN HDL Transmitter block oversamples the generated LUT data by 2 for better spectral efficiency and introduces a known carrier frequency offset (CFO).

The WLAN HDL Receiver block receives the WLAN packet and outputs the decoded information and the header and data constellation plots. The WLAN HDL Receiver block downsamples the received data by 2 and uses the HDL Implementation of WLAN Receiver (Wireless HDL Toolbox) example as a reference to decode the WLAN packets. The WLAN HDL Receiver block decodes the WLAN packet by using time and frequency synchronization, OFDM demodulation, channel estimation and equalization, format detection, signal decoding, and data decoding.

Hardware Generation Model

The zynqRadioHWSWWLANAD9361AD9364SL.slx model is a hardware generation model of the WLAN transmitter and receiver algorithm for targeting the software-defined radio (SDR) platform. From this model, you can generate HDL code for the programmable logic (PL) and generate a template software interface model by using the HDL Workflow Advisor app. You can use the template software interface model to generate an application that runs on the processing subsystem (PS). This diagram shows the hardware subsystem and a sample test harness.

Open the model by entering:

open_system('zynqRadioHWSWWLANAD9361AD9364SL.slx')

Hardware-Software Partitioning

The WLAN HDL subsystem contains the functionality to be implemented on the PL. The ARM processor reads the decoded WLAN information from the FPGA and displays the information on the host system.

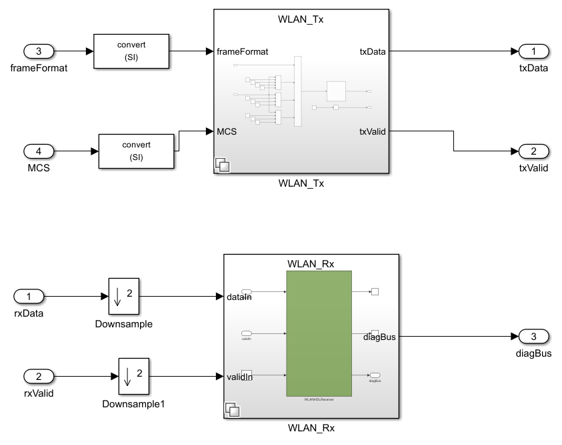

The WLAN_Tx_Rx subsystem contains the WLAN_Tx and WLAN_Rx subsystem. WLAN_Tx is a variant subsystem and it contains WLAN_Tx and WLAN_Tx_HighMCS subsystems that are implemented using LUTs.

The WLAN_Tx subsystem contains LUT data corresponding to modulation and coding schemes (MCS) from 0 to 3 for non-HT, from 0 to 2 for HT, and (VHT) frame formats.

The WLAN_Tx_HighMCS subsystem contains LUT data corresponding to modulation and coding schemes (MCS) from 0 to 7 for non-HT, HT, and VHT frame formats.

The wlanTxLUTDataGeneration.m and WLANHighMCS_TxLUTDataGeneration.m script uses the wlanWaveformGenerator function to generate the 20 MHz WLAN transmit waveform. The script oversamples the generated transmit waveform by 2 and adds 10 KHz CFO to the oversampled data. The WLAN_Tx subsystem transmits the oversampled data using the LUTs. In this example, the WLAN transmit waveform is generated for the following cases.

Frame Format Supported MCS PSDU Length APEP Length CFO in KHz

____________ ______________ _________________ ___________ __________

Non-HT {0,1,2,3} {100,100,100,100} - 10

HT-MF {0,1,2} {100,100,100} - 10

VHT {0,1,2} {101,101,104} 100 10

Frame Format Supported MCS APEP Length CFO in KHz

____________ _________________ ___________ __________

Non-HT {0,1,2,3,4,5,6,7} - 10

HT-MF {0,1,2,3,4,5,6,7} - 10

VHT {0,1,2,3,4,5,6,7} 200 10

Simulate Hardware Generation Model

Because the model contains many HDL-optimized blocks, which require simulation using sample-based signals, the simulation may take a while. After the simulation starts, double-click the Control Scope subsystem to view the Header and Data Constellation plots. You can view the decoded parameters, such as the frame format, MCS, PSDU length, signal parity, signal CRC, packet detected status, and estimated frequency offset (in Hz), by using the Display blocks.

When the simulation behavior of the hardware subsystem is as expected, generate the HDL IP core, integrate the generated IP core with the SDR reference design, and generate the software for the ARM processor.

Generate IP Core

By default the model supports lower MCS schemes from 0 to 3 for non-high-throughput (non-HT), from 0 to 2 for high-throughput (HT), and very-high-throughput (VHT) frame formats. To enable support for higher order MCS, double click on Higher MCS Support subsystem available at top right corner.

To generate the HDL IP core, right-click the WLAN HDL subsystem and select HDL Code > HDL Workflow Advisor.

Expand 1. Set Target and click 1.1. Set Target Device and Synthesis Tool. In the right pane, set Target workflow to

IP Core Generationand Target platform toZC706 and FMCOMMS2/3/4.

CASE 1: Higher MCS Support is disabled

Click 1.2. Set Target Reference Design. In the right pane, set Reference design to

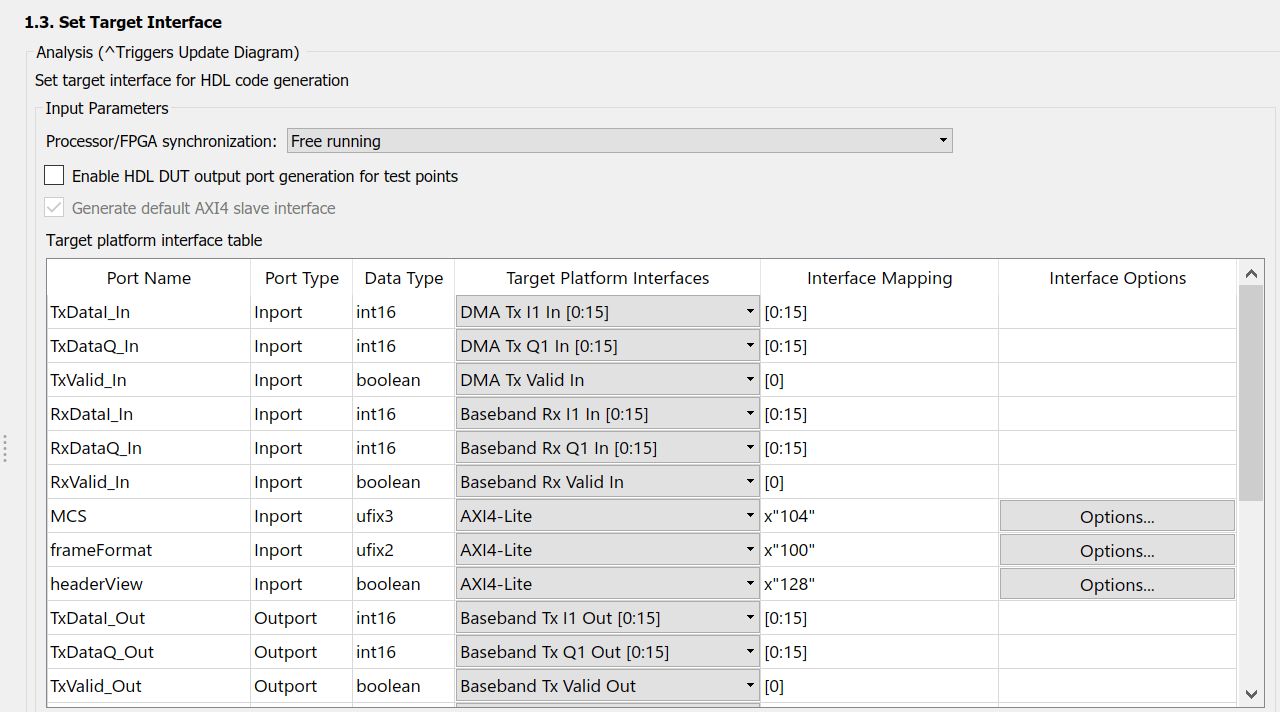

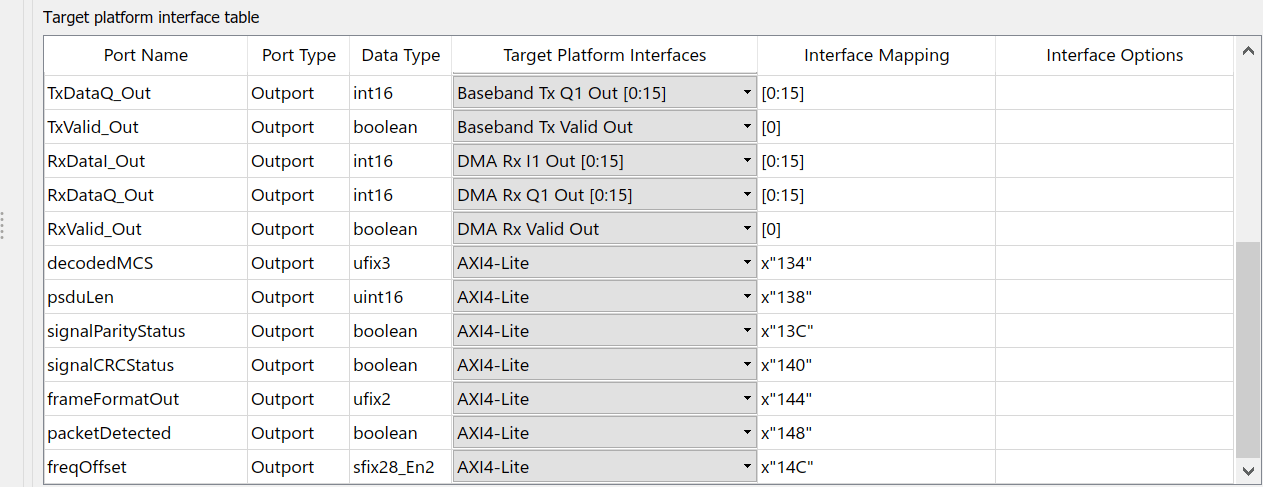

Receive and Transmit path. For this example, use the default settings in the Reference design parameters pane.Click 1.3. Set Target Interface. In the right pane, under the Target platform interface table pane map the DUT signals to the interface signals available in the reference design. Because this example uses a single channel, configure the channel 1 connections and AXI register interfaces as shown in these figures.

Click 1.4. Set Target Frequency. In the right pane, set Target Frequency (MHz) to

40. The DUT synthesis frequency depends on the baseband sampling rate of the system. The WLAN algorithm implementation in this example is built for a sampling rate value of 40 MHz.

CASE 2: Higher MCS Support is enabled

Click 1.2. Set Target Reference Design. In the right pane, set Reference design to

Receive and Transmit path with higher clock frequency.

Click 1.3. Set Target Interface. In the right pane, under the Target platform interface table pane, map the DUT signals to the interface signals available in the reference design.

Use the following settings in the Reference design parameters pane.

Baseband Sample Rate : 40

OverClocking Factor : 4

DUT Clock Frequency : 160

Click 2. Prepare Model for HDL Code Generation. In the right pane, click Run All. The app prepares the model for HDL code generation by performing design checks.

Click 3. HDL Code Generation. In the right pane, click Run All. The app generates HDL code for the IP core.

Next, continue to use the HDL Workflow Advisor to generate the software interface model and block library.

Generate Software Interface Model and Block Library

Expand 4. Embedded System Integration. This step integrates the newly generated IP core project into the Zynq SDR reference design, generates the corresponding bitstream, and loads the bitstream onto the board.

Click 4.1. Create Project. In the right pane, click Run This Task. The app creates a project for the embedded system tool.

Click 4.2. Generate Software Interface. In the right pane, click Run This Task. The app generates a software interface library and a template software interface model.

Software Interface Library

The app generates a new software interface library that contains a AXI Interface block generated from the WLAN HDL subsystem. This block shows the AXI-lite control ports, but not the data ports. The data ports on the AD936x Receiver and AD936x Transmitter blocks correspond to the hardware you selected in the 1.1. Set Target Device and Synthesis Tool pane in the HDL Workflow Advisor. The data ports represent the streaming data interface between the FPGA user logic and ARM processor.

When using the library blocks in a downstream model, you must configure the parameters correctly for your application. Consider that any updates to the WLAN HDL subsystem are automatically propagated to the library blocks in the downstream model when you again run the task in 4.2. Generate Software Interface in the HDL Workflow Advisor.

Template Software Interface Model

The app generates a new template software interface model. Use this model as a starting point for full software targeting. You can simulate the model in external or full deployment mode. Because HDL Workflow Advisor overwrites the generated model each time you run the task in 4.2. Generate Software Interface, consider saving the generated model under a unique name and developing your software algorithm.

Next, continue to use the HDL Workflow Advisor to generate and load the bitstream.

Generate and Load Bitstream

The last steps of the HDL Workflow Advisor generate a bitstream for the PL and download the bitstream onto the board.

Click 4.3. Build FPGA Bitstream. In the right pane, click Run This Task. The app generates a bitstream for the PL. You can execute this step in an external shell by selecting Run build process externally. This selection allows you to continue using MATLAB while building the FPGA image. After the basic project checks complete, the app marks this check with a green checkmark. However, you must wait until the external shell displays a successful bitstream build before moving on to the next step.

Click 4.4. Program Target Device. In the right pane, click Run This Task. The app downloads the bitstream onto the device. Before continuing with this step, call the

zynqfunction to ensure that MATLAB has the correct physical IP address for the radio hardware:

>> devzynq = zynq('linux','192.168.3.2','root','root','/tmp');

By default, '192.168.3.2' is the physical IP address of the radio hardware. If you change the radio hardware IP address during the hardware setup process enter the corresponding address.

Alternatively, if you want to load the bitstream outside the HDL Workflow Advisor, create a SDR radio object by using sdrdev object and use the downloadImage function. The type of object you create depends on the Target platform setting in the 1.1. Set Target Device and Synthesis Tool pane.

If the target platform is ZC706 and FMCOMMS2/3/4, create an sdrdev object using the 'AD936x' input argument.

>> radio = sdrdev('AD936x');

Download the bitstream by using the radio object and interfacing the selected radio device.

>> downloadImage(radio,'FPGAImage', ... 'hdl_prj\vivado_ip_prj\vivado_prj.runs\impl_1\system_top.bit') % Path to the generated bitstream

WLAN Software Interface Model

The software interface model is based on the generated template software interface model. The model displays the decoded status information: MCS, PSDU length, signal parity status, signal CRC status, frame format, packets detected, and the estimated frequency offset from the WLAN HDL subsystem. The model also plots the real time data or header constellation diagram based on the headerView control signal.

Open the model by entering:

open_system('zynqRadioHWSWWLANAD9361AD9364SL_interface')

The model is configured for the Xilinx Zynq-7000 Based IIO Radio target. You can use this target for the ZC706 and FMCOMMS2/3/4/5 radio platform.

Run Design on Zynq Board

You can run the WLAN software interface model by selecting Monitor & Tune mode in RUN ON HARDWARE section of Simulink Toolstrip. In this mode, you can control the configuration from the Simulink model. Alternatively, to deploy the design on the board disconnected from Simulink, select Build, Deploy & Start in DEPLOY section of Simulink Toolstrip.

Host Interface Model

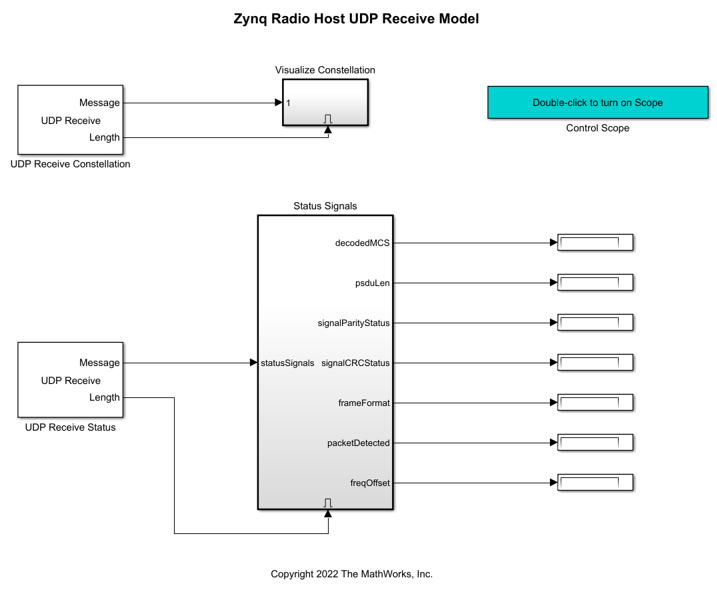

The ARM processor sends the WLAN receiver output data and decoded status signals directly to the host over the Ethernet link by using the UDP Send blocks. The IP address of the UDP Send blocks must be same as the IP address of the host. By default, this value is '192.168.3.1'. If you alter the IP address during the hardware setup process change the address. This interface model that runs on the host illustrates how to receive data from the hardware platform using the UDP Receive blocks and how to postprocess it.

Open the model by entering:

open_system('zynqRadioHWSWWLANAD9361AD9364SL_UDP_Receive')

When the host interface model successfully runs, the model displays the receiver status signals information from the FPGA.

CASE 1: Higher MCS Support is disabled

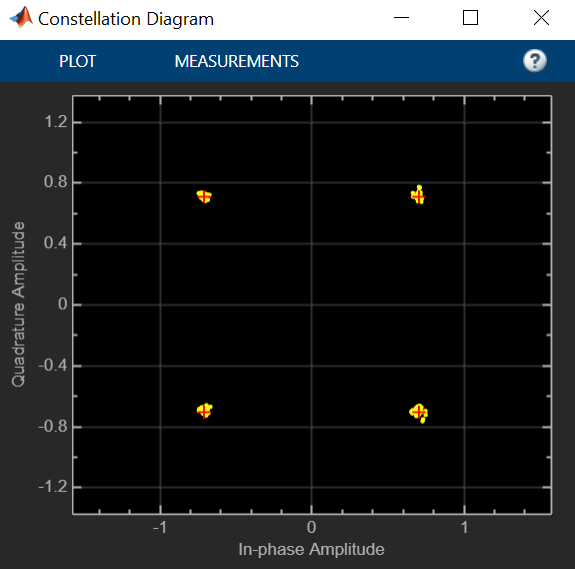

To see the constellation plot, double-click the Control Scope subsystem. By default, the software interface model sets the MCS block to 2, the frameFormat block to HT-MF, and the headerView block to false.

This figure shows the constellation plot when the headerView input is set to true.

CASE 2: Higher MCS Support is enabled

If bitstream generation occurs after enabling Higher MCS Support, change the MCS value to see the corresponding modulation coding scheme and constellation output.

See Also

Topics

- Hardware-Software Co-Design Workflow

- HDL Implementation of WLAN Receiver (Wireless HDL Toolbox)