PLL

(To be removed) Determine frequency and fundamental component of signal phase angle

The Specialized Power Systems library will be removed in R2026a. Use the Simscape™ Electrical™ blocks and functions instead. For more information on updating your models, see Upgrade Specialized Power Systems Models to use Simscape Electrical Blocks.

Libraries:

Simscape /

Electrical /

Specialized Power Systems /

Control

Description

The PLL block models a Phase Lock Loop (PLL) closed-loop control system, which tracks the frequency and phase of a sinusoidal signal by using an internal frequency oscillator. The control system adjusts the internal oscillator frequency to keep the phases difference to 0.

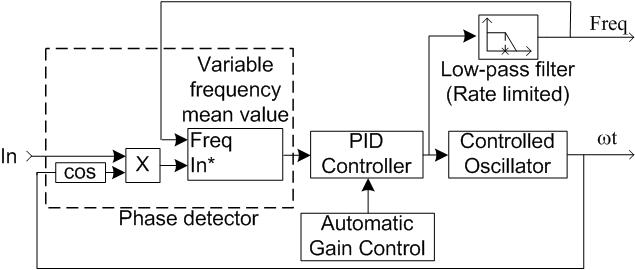

The figure shows the internal diagram of the PLL.

The input signal is mixed with an internal oscillator signal. The DC component of the mixed signal (proportional to the phase difference between these two signals) is extracted with a variable frequency mean value. A Proportional-Integral-Derivative (PID) controller with an optional automatic gain control (AGC) keeps the phase difference to 0 by acting on a controlled oscillator. The PID output, corresponding to the angular velocity, is filtered and converted to the frequency, in hertz, which is used by the mean value.

Characteristics

| Sample Time | Specified in the Sample Time

parameter. Continuous when Sample Time = 0. |

| Scalar Expansion | No |

| Dimensionalized | No |

| Zero-Crossing Detection | Yes |

Ports

Input

Output

Parameters

Extended Capabilities

Version History

Introduced in R2013a