Sinusoidal Measurement (PLL, Three-Phase)

Estimate three-phase sinusoidal characteristics using a phase-locked loop

Libraries:

Simscape /

Electrical /

Control /

Measurements

Description

The Sinusoidal Measurement (PLL, Three-Phase) block estimates the frequency characteristics of a balanced three-phase sinusoidal signal. The block uses a standard phase-locked loop (PLL) strategy to estimate the frequency and phase angle of the input signal. It also outputs the magnitude of the input signal.

Use this block in control applications when the frequency, phase angle, or magnitude are required and cannot be measured directly. To estimate the frequency characteristics of a non-three-phase or unbalanced sinusoidal signal, use the Sinusoidal Measurement (PLL) block instead.

Equations

The phase-locked loop generates a sinusoid that approximates the input signal u(t) with the form:

where:

y is the estimate of the input signal.

A is the amplitude of the input signal.

ϕ0 is the initial phase angle of the input signal.

Because the input signal is assumed to be balanced, the block calculates the amplitude directly from the instantaneous amplitude of the three phases. The estimated phase angle ϕ is the angle of this generated sinusoid:

where f if the frequency of the sinusoid, and ϕ0 is the initial phase angle.

This diagram shows the overall structure of the phase-locked loop.

In the diagram:

The phase detector produces an error signal relative to the phase difference eϕ between the input sinusoid u and the synthesized sinusoid y. It also outputs the amplitude A.

The loop filter provides an estimate of the input angular frequency ω by filtering out the high-frequency components of the phase difference. The block also outputs the converted frequency f in Hz.

The voltage-controlled oscillator integrates the angular speed to produce the phase estimate ϕ which it sends to the Phase Detector for comparison.

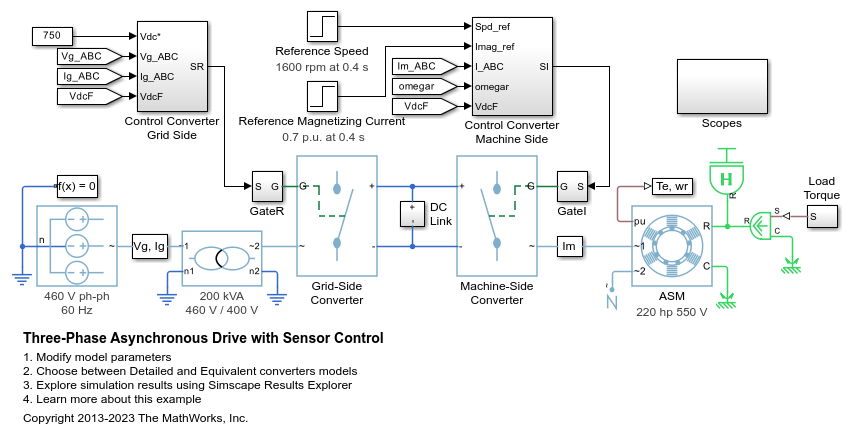

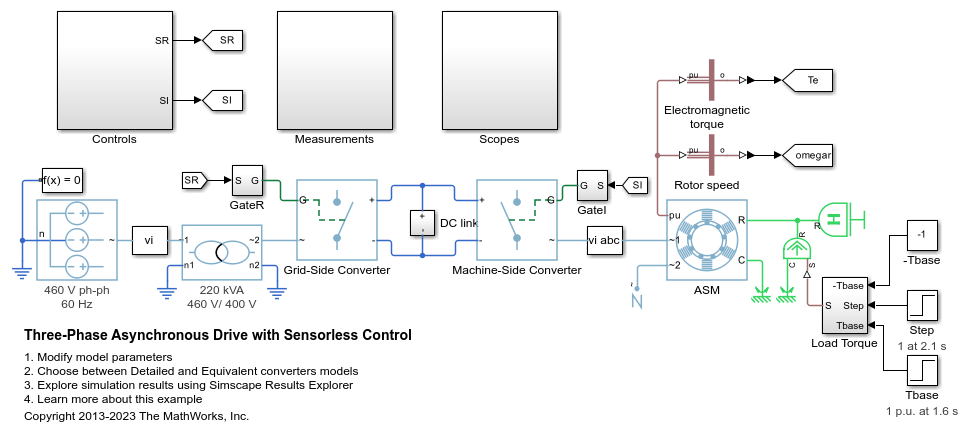

Examples

Assumptions and Limitations

The input signal, u, must not have a DC bias and must be in this form: