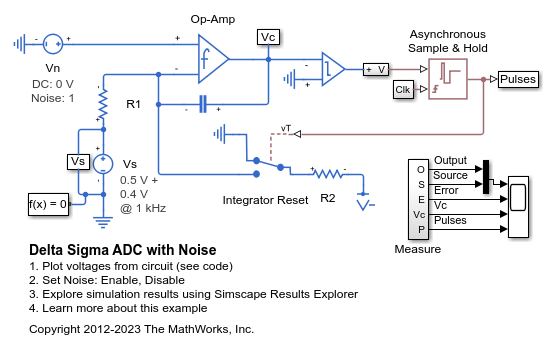

Delta Sigma ADC with Noise

This example shows a simple implementation of a sigma delta analog-to-digital converter. An input in the range 0 to Vref (=1V) is integrated until it causes the integrator to reset. The time to reset is proportional to the input value. Demodulation of the pulses is performed by a low-pass filter. The Asynchronous Sample & Hold block behaves like an edge-triggered D-type flip-flop, passing input U to output Y only on a rising edge of the clock. This model can be used to explore and understand the effect of op-amp impairments such as equivalent input noise on converter accuracy. To turn off the noise, open block Vn and select 'Disabled' for the noise mode.

The Solver Configuration block is set to use the fixed-step trapezoidal Simscape™ local solver. This is selected for simulation speed. The simulation step size is parameterized by workspace parameter Tsim, the value of which should be increased from some small value until the point where results are affected. The parameter Tsim also sets the noise sample time in block Vn.

Model

Simulation Results from Simscape Logging

The plot below shows the outputs of the Delta Sigma converter circuit.

See Also

Band-Limited Op-Amp | Comparator | SPDT Switch