F28P65x 内存配置

F28P65x 设备的内存配置与其前代产品略有不同。F28P65x 设备有五个闪存块,您可以将其分配给 CPU1 或 CPU2。此外,CPU1 或 CLA 可以使用 LS RAM,而 RAM Dx 内存可以映射到 CPU1 或 CPU2。

闪存块配置

在 C2000™ Microcontroller Blockset 中,闪存块 0-2 分配给 CPU1,闪存块 3 和 4 分配给 CPU2。

如果您在 CCS 工具中没有对闪存块进行类似的配置,则在 CCS 工具中从外部下载 Simulink® 生成的 .out 文件时,可能会遇到以下错误。在 Simulink 中下载代码时不会出现此错误:

C28xx_CPU2: Flash Programmer: Error erasing Bank 0 FMSTAT (STATCMD on some devices) value = 65. Operation Cancelled (0). C28xx_CPU2: File Loader: Memory write failed: Unknown error C28xx_CPU2: GEL: File: <generated .out file>: Load failed.

在 CCS 工具中配置闪存块

请按照以下步骤在 CCS 工具中配置闪存块:

右键点击 F28P65x 设备的 ccxml 文件,然后选择启动选定配置打开调试视图。

在调试视图中,选择核心 C28xx_CPU1,然后导航到工具 > 片上闪存,打开 CPU1 闪存插件 GUI。

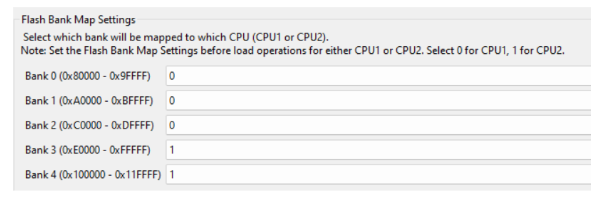

在 CPU1 闪存插件 GUI 中,在 Flash Bank Map Settings 下,将 Bank 0, 1, and 2 映射到 CPU1,将 Bank 3 and 4 映射到 CPU2,如图所示。

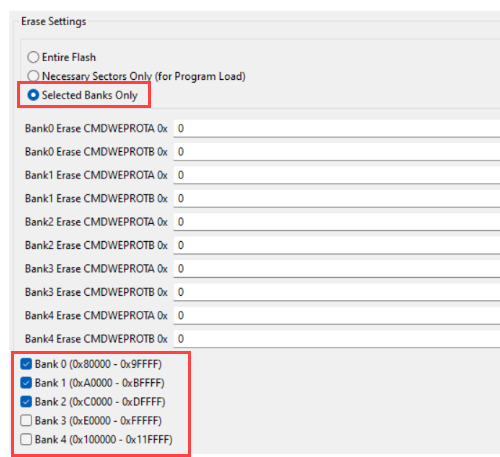

在 GUI 中导航到 Erase Settings 部分,并启用闪存块 0、1 和 2 作为 CPU1 闪存插件可以擦除的库,如图所示。

导航到 CPU1 flash 插件 GUI 的顶部,然后使用 Configure Clock 按钮设置 PLL。在执行任何 CPU2 闪存插件操作(包括将可执行文件加载到 CPU2 闪存)之前,请确保完成此步骤。

4o现在,在调试视图中,选择核心 C28xx_CPU2,然后导航到菜单选项 Tools > On_Chip Flash。此操作将打开 CPU2 闪存插件 GUI。

与步骤 3 和 4 类似,在 CPU2 闪存插件 GUI 中,将 Bank 0-2 映射到 CPU1,将 Bank 3 和 4 映射到 CPU2。此外,在 Erase settings 下,启用 Bank 3 和 Bank 4,以便 CPU2 的 flash 插件可以擦除它们。

为确保 CCS 记住您在 Flash 插件 GUI 中配置的设置,点击 GUI 底部的 Remember My Settings 按钮。此操作会将您的设置保存到下次迭代中。

RAM D 内存配置

C2000 Microcontroller Blockset 中为 F28P65x 设备提供的 .cmd 文件将 RAM D 内存划分如下:RAMD0 和 RAMD1 分配给 CPU1,而 RAMD2 到 RAMD5 分配给 CPU2。

LS RAM 配置

LS RAM 内存仅供 CPU1 和 CLA 访问。您可以在模型配置参数中配置此内存分配。导航至 Hardware Implementation > Target hardware resources > Build 选项并选择 Configure CLA program and data memory。