PIL 仿真

处理器在环 (PIL) 仿真在您的开发计算机上交叉编译源代码,然后将目标代码下载到硬件板中的处理器上并运行。借助 SoC Blockset™ 和 C2000™ Microcontroller Blockset 功能,您可以在支持的 Texas Instruments® 硬件板上运行模型的部分内容,从而直接从处理器获取算法和任务执行时间的测量结果。这些测量结果可用于提高仿真的质量。

SoC Blockset 模型和支持的 Texas Instruments 硬件板可以使用两种类型的 PIL 仿真:模块级仿真和顶层模型仿真。这些章节描述了使用 SoC Blockset 模型时可用的两种 PIL 仿真类型。有关 PIL 仿真的一般信息,请参阅 SIL 和 PIL 仿真 (Embedded Coder)。

注意

使用 C2000 Microcontroller Blockset 进行 PIL 仿真仅支持使用 SCI_A 通信通道。

模块级 PIL 仿真

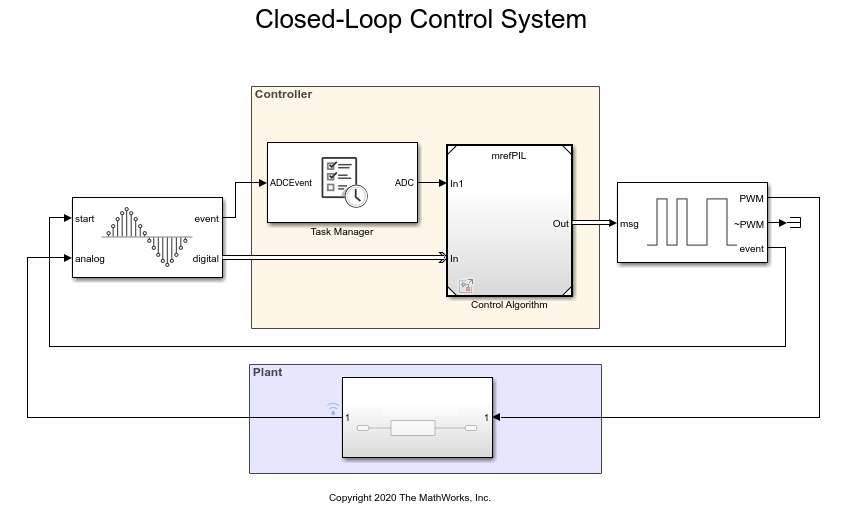

打开一个 C2000 Microcontroller Blockset 模型,例如图中所示的闭环控制系统。

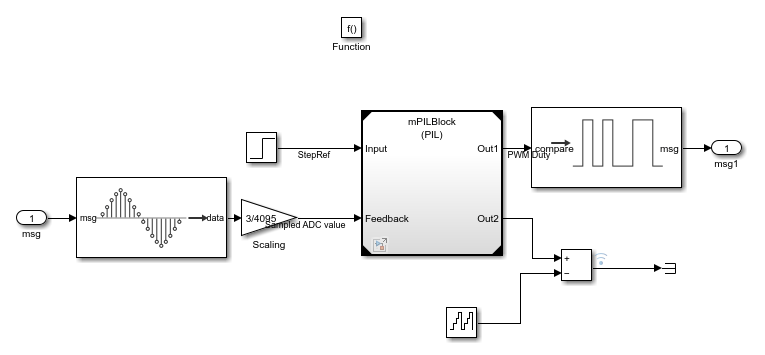

打开代表硬件板上 CPU1 的控制算法参考模型。有关为参考模型选择 CPU 的更多信息,请参阅 硬件板设置。控制算法 mPILBlock 是参考模型模块使用的一个独立模型。mPILBlock 参考模型连接到 ADC Read (SoC Blockset) 和 PWM Write (SoC Blockset) 模块,但自身不包含任何驱动模块。

选择 mPILBlock 参考模型。在模型模块选项选项卡上,将仿真模式设置为处理器在环(PIL)。

在 App 选项卡上的代码验证、确认和测试下,点击 SIL/PIL 管理器。

在 SIL/PIL 选项选项卡上,将在测系统设置为 SIL/PIL 模式下的 Model 模块。将 mPILBlock 模型模块配置为 PIL 操作,然后仅为该参考模型模块生成代码,并将其部署到硬件板上的处理器。

(可选)生成 PIL 任务探查报告。在 SIL/PIL 选项卡上,展开设置并启用任务探查。

在 SIL/PIL 选项卡上,点击 Run SIL/PIL 运行仿真。

顶层 PIL 仿真

在顶层 PIL 仿真中,为顶层参考模型生成代码,然后将其部署到连接的硬件板上并执行。有关配置顶层 PIL 仿真的详细说明,请参阅 配置并运行 PIL 仿真 (Embedded Coder)。

当在 C2000 Microcontroller Blockset 模型上使用顶层 PIL 仿真时,顶层参考模型在硬件板的处理器上执行。然而,由于 PIL 设置的混合性质,该模型必须满足这些限制。

所有任务都必须由计时器驱动。不支持事件驱动型任务。

无法向模型模块发送消息。因此,这些模型中无法使用驱动模块。

另请参阅

SIL 和 PIL 仿真 (Embedded Coder) | PIL Simulation Sequence (Embedded Coder) | 硬件板设置 | 配置并运行 PIL 仿真 (Embedded Coder)