Histogram

Frequency distribution of pixel values in video stream

Libraries:

Vision HDL Toolbox /

Statistics

Description

The Histogram block computes the frequency distribution of pixel values in a video stream. You can configure the number and size of the bins. The block provides a read interface for accessing each bin. The block keeps a running histogram until you reset the bin values.

Examples

Histogram Equalization

Use the Vision HDL Toolbox™ Histogram library block to implement histogram equalization.

Ports

This block uses a streaming pixel interface with a bus for frame control signals. This interface enables the block to operate independently of image size and format. All Vision HDL Toolbox™ blocks use the same streaming interface. The block accepts a scalar pixel value and a bus that contains five control signals. The control signals indicate the validity of each pixel and its location in the frame. To convert a frame (pixel matrix) into a pixel stream and control signals, use the Frame To Pixels block. For a full description of the interface, see Streaming Pixel Interface.

Input

This block supports single pixel streaming or multipixel streaming. For single pixel streaming, specify a single input pixel as a scalar intensity value. For multipixel streaming, specify a vector of two, four, or eight pixel intensity values. For details of how to set up your model for multipixel streaming, see Filter Multipixel Video Streams.

This block does not support multicomponent streaming. To process

multicomponent streams, replicate the block for each component. The

pixelcontrol bus for all components is identical,

so you can connect a single bus to multiple replicated blocks.

The software supports double and

single data types for simulation, but not for HDL code generation.

Data Types: uint | fixdt(0,W,0) | Boolean | double | single

The pixelcontrol bus contains five signals.

The signals describe the validity of the pixel and its location in the frame. For more

information, see Pixel Control Bus.

For multipixel streaming, each vector of pixel values has one set of control signals.

Because the vector has only one valid signal, the pixels in the

vector must be either all valid or all invalid. The hStart and

vStart signals apply to the pixel with the lowest index in the

vector. The hEnd and vEnd signals apply to the

pixel with the highest index in the vector.

Data Types: bus

The block captures this value each cycle that the

readRdy output port is 1

(true). The data type is

fixdt(0,W,0), W = 5,6,...,12. The word length

must be log2(Number of

bins).

Data Types: fixdt(0,W,0)

A binReset value of 1 (true)

triggers a RAM initialization sequence that resets the histogram bin

values. Reset takes NumBins cycles to clear all

locations. Input signals are ignored during this interval.

Data Types: Boolean

Output

When readRdy is 1 (true), the

histogram bins are ready to read. The block returns

readRdy set to 1 (true) two

cycles after the final pixel of a frame.

Data Types: Boolean

Histogram bin value corresponding to the requested address, binAddr. The Data type parameter specifies the data type for this value.

Data Types: fixed point

When validOut is 1 (true), the

histogram bin value, hist, is valid.

Data Types: Boolean

Parameters

Choose the number of bins depending on the input word length (WL). If the number of bins is less than 2WL, the block truncates the least-significant bits of each pixel. If the number of bins is greater than 2WL, some bins are not used, and after you synthesize your design it will use more hardware resources than necessary.

Data type of histogram bin values.

The software supports double and

single data types for simulation, but not for HDL code generation.

Word length of the histogram bins. If a bin overflows, the count saturates and the block shows a warning.

Dependencies

This parameter applies when you set Data type to

Unsigned fixed point.

Algorithms

Before sending the first input data, you must wait Number of bins cycles for the block to reset the RAM. This initial reset happens without asserting binReset.

You cannot read histogram bins and apply pixel data at the same time. To read the

bin values, wait for the readRdy port to be 1

(true), and then apply each bin address of interest to the

binAddr port. The block provides the corresponding

histogram values on the hist port, with an accompanying

validOut signal.

The histogram values persist and accumulate across frames until you assert binReset. At that time, the block takes Number of bins cycles to clear the RAM and be ready for new input. Other input signals are ignored during reset.

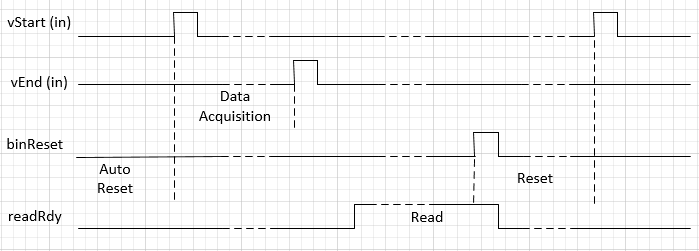

The diagram shows an overview of the reset sequence. vStart and

vEnd are control signals in the

pixelcontrol input bus.

The diagram shows the automatic startup reset, followed by a frame of video input. The read window starts when readRdy is asserted. The binReset signal initiates a bin reset. The next input frame is not applied until after the reset is complete.

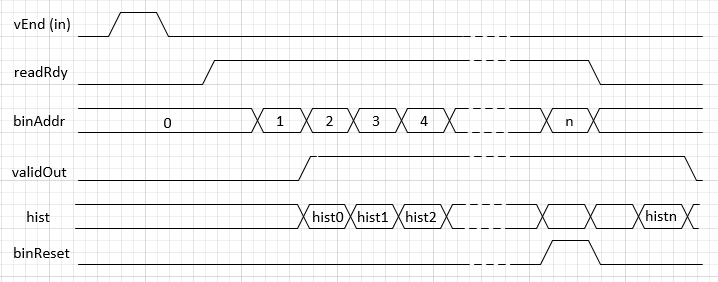

The following diagram illustrates a bin read sequence. vEnd is

a control signal in the pixelcontrol input bus.

validOut indicates when the bin values on

hist are available.

After the last pixel of a video frame, indicated by vEnd =

true, the block asserts readRdy to show

that the histogram is ready for reading. Two cycles after applying a bin address,

the block provides the value of that bin on hist, with a

corresponding valid signal. You can request the last bin address and assert

binReset at the same time.

The block sets readRdy to true two cycles

after receiving the last pixel of a frame. The input pixelcontrol

bus indicates the last pixel of a frame by vEnd =

true. While readRdy is

true, the block captures binAddr

requests on each cycle. The block provides the corresponding histogram bin values on

hist two cycles later.

This table shows the resource use after synthesis of the block for the Xilinx®

Zynq®-7000 SoC ZC706 Evaluation Kit with single-pixel

uint8 input and the default parameter settings. The design

achieves a clock frequency of 322 MHz.

| Resource | Usage |

|---|---|

| Slice LUTs | 293 |

| Slice Registers | 274 |

| DSP48 | 0 |

| Block RAM | 0 |

Extended Capabilities

This block supports C/C++ code generation for Simulink® accelerator and rapid accelerator modes and for DPI component generation.

HDL Coder™ provides additional configuration options that affect HDL implementation and synthesized logic.

This block has one default HDL architecture.

| ConstrainedOutputPipeline | Number of registers to place at

the outputs by moving existing delays within your design. Distributed

pipelining does not redistribute these registers. The default is

|

| InputPipeline | Number of input pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| OutputPipeline | Number of output pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| SynthesisAttributes |

Specifies the synthesis attributes for the blocks and block output signals in the model. The generated HDL code contains these attributes. For more information, see SynthesisAttributes (HDL Coder). |

You cannot generate HDL for this block inside a Resettable Synchronous Subsystem (HDL Coder).

Version History

Introduced in R2015aThe block now supports multipixel streams that have 2 pixels per clock cycle.

The Histogram block now supports multipixel streams. The HDL implementation replicates the algorithm for each pixel in parallel.

The block supports input column vectors of NumPixels values,

where NumPixels is 4 or 8. The ctrl ports

remain scalar, and the control signals in the pixelcontrol bus

apply to all pixels in the matrix. The output interface is the same whether the

input is scalar or vector.

You can now configure the block to have 2048 or 4096 histogram bins.

See Also

Blocks

- 2-D Histogram (Computer Vision Toolbox) | Frame To Pixels

Objects

Functions

imhist(Image Processing Toolbox)

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

选择网站

选择网站以获取翻译的可用内容,以及查看当地活动和优惠。根据您的位置,我们建议您选择:。

您也可以从以下列表中选择网站:

如何获得最佳网站性能

选择中国网站(中文或英文)以获得最佳网站性能。其他 MathWorks 国家/地区网站并未针对您所在位置的访问进行优化。

美洲

- América Latina (Español)

- Canada (English)

- United States (English)

欧洲

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)