Design and Verification of Xilinx FPGAs and SoCs Using MATLAB and Simulink

In these webinars, MathWorks, Xilinx, and Avnet engineers demonstrate how HDL code generation and verification tools from MATLAB® and Simulink® can significantly accelerate your FPGA design cycle. Through a series of demonstrations, the presenters show how to build system models in Simulink, elaborate models for FPGA implementation, apply optimizations for improved timing and reduced FPGA resource usage, and verify implementations using accelerated hardware simulation—also known as FPGA-in-the-loop—on Xilinx development boards.

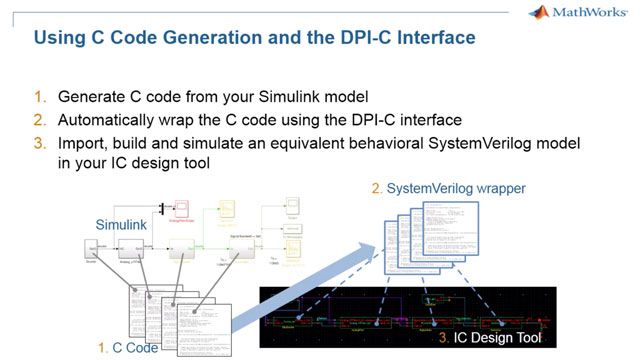

Generate SystemVerilog DPI for Analog Mixed-Signal Verification

Export analog/mixed-signal Simulink models into your SystemVerilog simulator.