Rambus 使用高级综合工具和 HDL Coder 开发用于 ASIC 的 DSP 模块

“通常,在基于规范的第一个 RTL 版本准备就绪之前,验证和后端团队不能开始集成工作,因为该版本可能仍有缺陷。借助基于 HDL Coder 的工作流,只需点击一下按钮,即可从系统级验证模型中生成 HDL 代码,这不仅帮助节省了数月的时间,而且还确保这些团队拥有高质量的起点。”

关键成果

- 通过使用 HDL 代码生成,设计过程的时间从一年大幅缩短到了三个月,同时工作效率得到了提升,保留在最终实现中的生成代码也达到了 80%

- 验证环境开发从自动生成的 RTL 代码开始,与自定义 RTL 开发齐头并进

- 在各代设计或同代实现之间转换时,需要对支持 HDL 的 Simulink 模型进行的更改很少

当今的通信设备集成了专用集成电路 (ASIC) 中实现的复杂信号处理算法,可以提高性能并降低最终产品成本和功耗。ASIC 的物理实现过程相当漫长。此过程在 RTL 验证完成之前开始,需要手动集成优化的加法器和乘法器,以及 RTL 调试和可观测性功能。

身为 Rambus 的数字工程总监,Ehud Nir 需要在时间和工程资源有限的情况下为 Gen6 PCIe PHY 开发 DSP。在之前的类似设计项目中,一位 ASIC 设计人员负责编写 RTL 代码,而另一位验证工程师负责开发测试平台。两人为此项目一起工作了 12 个月。鉴于系统架构师已使用 MATLAB® 和 Simulink® 对包括 DSP 在内的完整 Gen6 串行器/解串器 (SerDes) 进行建模,Ehud 决定尝试使用 HDL Coder™ 直接从 Simulink 模型为 ASIC 实现生成 RTL 参考,以便加速设计过程。

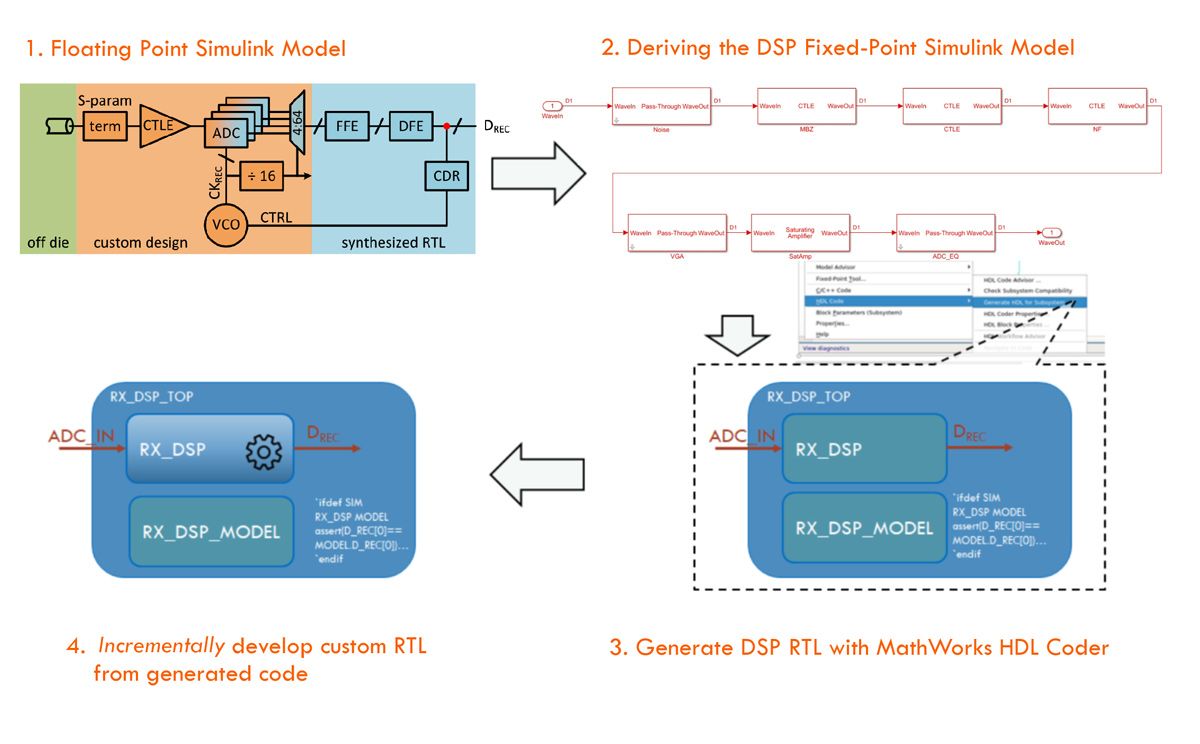

首先,系统架构师将 SerDes DSP 的 Simulink 浮点模型转换为定点模型。在确保该模型满足目标电气规范和特性要求后,ASIC 数字设计人员便使用 HDL Coder 从定点模型生成了 RTL 代码。由于需求不断变化,例如修改数字前端滤波器,在设计过程中,多次从 Simulink 中重新生成了该参考模型。

HDL Coder 所生成的 RTL 代码作为了参考点,供验证团队开始 IP 级验证以及后端团队开始进行物理设计。与此同时,数字设计人员通过开发组合和时序逻辑自定义 RTL 代码,以降低功耗并增加低功耗模式。使用生成的 RTL 作为参考,可在自定义的 RTL 和生成的 RTL 参考之间进行完整的层次比较。通过添加的断言,可以使用 HDL 仿真器检查自定义 RTL,以确保其位周期与参考模型的完全一致。因此,只需一位工程师在短短三个月之内就能制作出经过全面验证、时序清晰的 DSP 网表,而之前的项目需要两位工程师工作长达 12 个月。以此 DSP 为后盾的 Gen6 PHY ASIC 测试芯片,已在实验室进行了验证并取得了首过成功。