Vision Processing FPGA and ASIC Hardware Considerations | Vision Processing for FPGA, Part 1

From the series: Vision Processing for FPGA

Computer vision applications in automated driving often require fast processing to condition the incoming image data. FPGA or ASIC hardware accelerate vision processing, but algorithms need to be adapted to work on hardware. Learn about the high-level architecture of this hardware fabric, the constraints that must be met for efficient implementation, and how Vision HDL Toolbox™ helps you make the transition from algorithm to hardware. The topics covered in this video include:

- What parts of an automated driving application are typically implemented in hardware versus software

- The difference between processing frame-based data and a stream of pixels

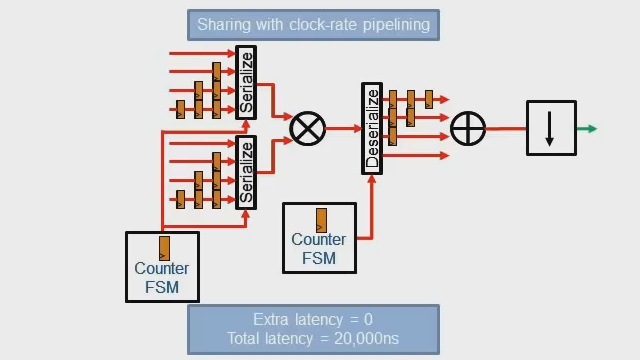

- FPGA and ASIC architectures and constraints

- Using line buffer memory to perform operations on a “region of interest” from a stream of pixels

- Why it’s important for video and image processing engineers to collaborate with hardware implementation engineers

Published: 14 Sep 2017