Code Verification and Validation with PIL

This example shows you how to use Embedded Coder® Support Package for Qualcomm® Hexagon® Processors for code verification and validation using PIL.

Introduction

Using this example, you can perform validation of processor-in-the-loop (PIL) in two different modeling scenarios:

Referenced model

Top model

In this example, you will learn how to configure a Simulink® model to run Processor-In-the-Loop (PIL) simulations. In a PIL simulation, the generated code runs on a Qualcomm Hexagon Processor. The results of the PIL simulation are transferred to Simulink to verify the numerical equivalence of the simulation and the code generation results. The PIL verification process is a crucial part of the design cycle to ensure that the behavior of the deployment code matches the design.

This example introduces the Simulink® code generation and verification workflow by showing you how to configure a Simulink model to run PIL simulations on the Qualcomm Hexagon Simulator.

Supported Hardware

Qualcomm Hexagon Simulator. For more information, see Qualcomm Hexagon Simulator Configurations.

Qualcomm Hexagon Android® Board. For more information, see Qualcomm Hexagon Android Board Configurations.

Qualcomm Hexagon Linux® Board. For more information, see Qualcomm Hexagon Linux Board Configurations.

Qualcomm Android Board. For more information, see Qualcomm Android Board Configurations.

Qualcomm Linux Board. For more information, see Qualcomm Linux Board Configurations.

Prerequisites

Launch hardware setup and install the required SDK. For more information, see the Launch Hardware Setup.

Required Hardware

To run this example, you will need the following hardware:

Supported Qualcomm Hexagon Simulator

Qualcomm Hexagon Android Board

Qualcomm Hexagon Linux Board

Qualcomm Android Board

Qualcomm Linux Board

Available Models

Verifying Referenced Model Code Using PIL

This example shows how to verify the generated code for a referenced model by running a PIL simulation. With this approach:

You can verify code generated for referenced models.

You must provide a test harness model to provide a test vector or stimulus inputs.

You can easily switch a Model block between normal and PIL simulation mode.

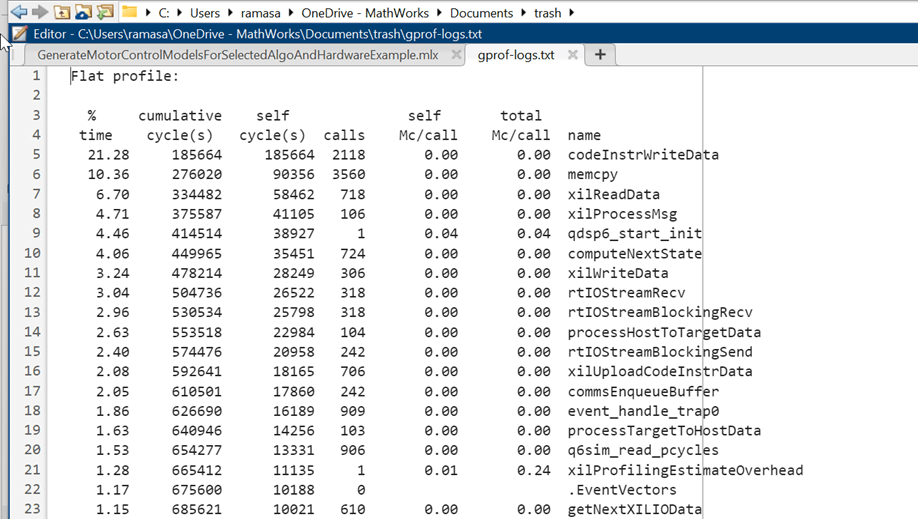

Open the hexagon_model_block_pil model. The model contains two model blocks that both point at the same referenced model. You will configure one of the model blocks to run in PIL simulation mode and the other in normal mode.

Configure and run CounterA model block in PIL simulation mode. Right-click on CounterA block and select Block Parameters (ModelReference). Select Simulation mode > Processor-in-the-loop (PIL) and click OK.

When the model starts running, Scope1 displays the PIL simulation output running on the Qualcomm Hexagon Simulator while Scope2 displays the normal mode simulation output.

Verifying Top Model Code Using PIL

This example shows how to verify the generated code for a model by running a PIL simulation. With this approach:

You can verify code generated for a top model.

You must configure the model to load test vectors or stimulus inputs from the MATLAB® workspace.

You can easily switch the entire model between normal and PIL simulation mode.

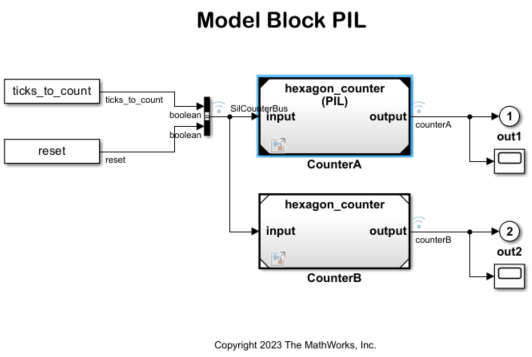

Open the hexagon_top_model_pil model in Simulink. This model is configured for running top-model-level PIL verification.

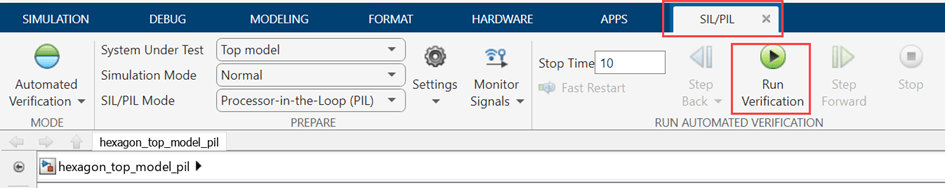

Run the top model PIL simulation. Open the Apps tab and select SIL/PIL Manager. On the SIL/PIL tab, select SIL/PIL Mode > Processor-in-the-loop(PIL) option and click Run Verification.

When the PIL simulation is completed, a

logsOutvariable is created in the base workspace. The logsOut data contains PIL simulation results. You can access the logged data forsignals count_aandcount_busing these commands:

count_a = get(logsOut,'count_a');

count_a.Values.Data

count_b = get(logsOut,'count_b');

count_b.Values.Data

Report Generation with Hexagon Profiler and gprof

This example shows how to generate report using Hexagon profiler and gprof for a model by performing a SIL/PIL Manager verification.

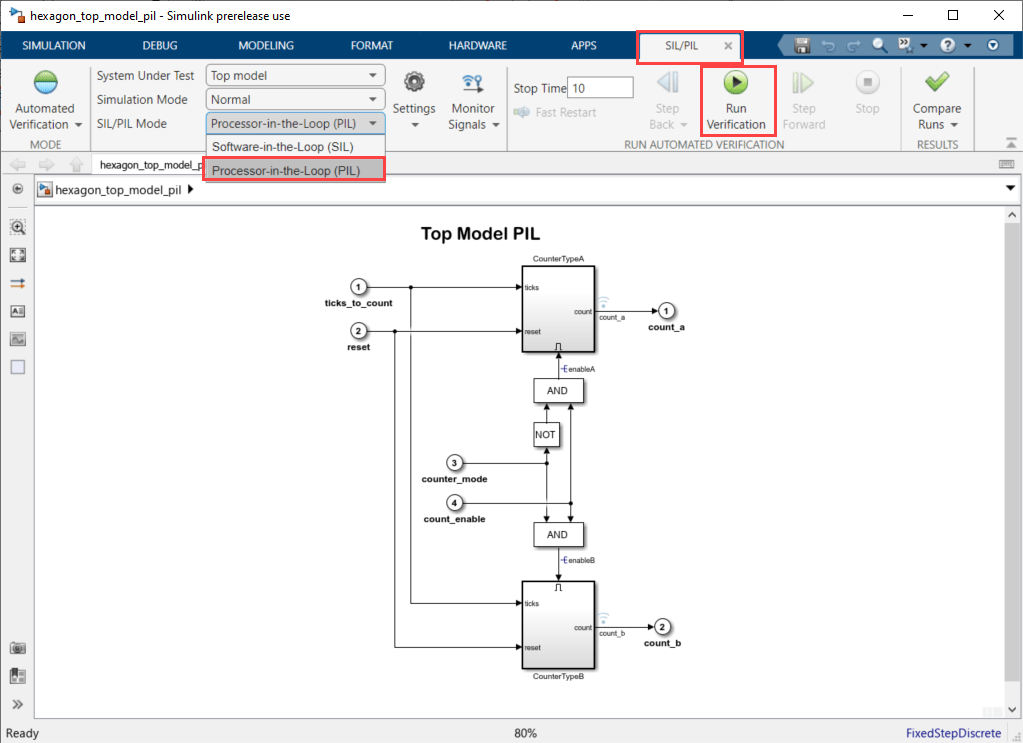

Open the hexagon_top_model_pil model.

Press Ctrl+E to open the Model Configuration. Set the device profiler to Hexagon profiler and gprof. For more information, see Qualcomm Hexagon Simulator Configurations.

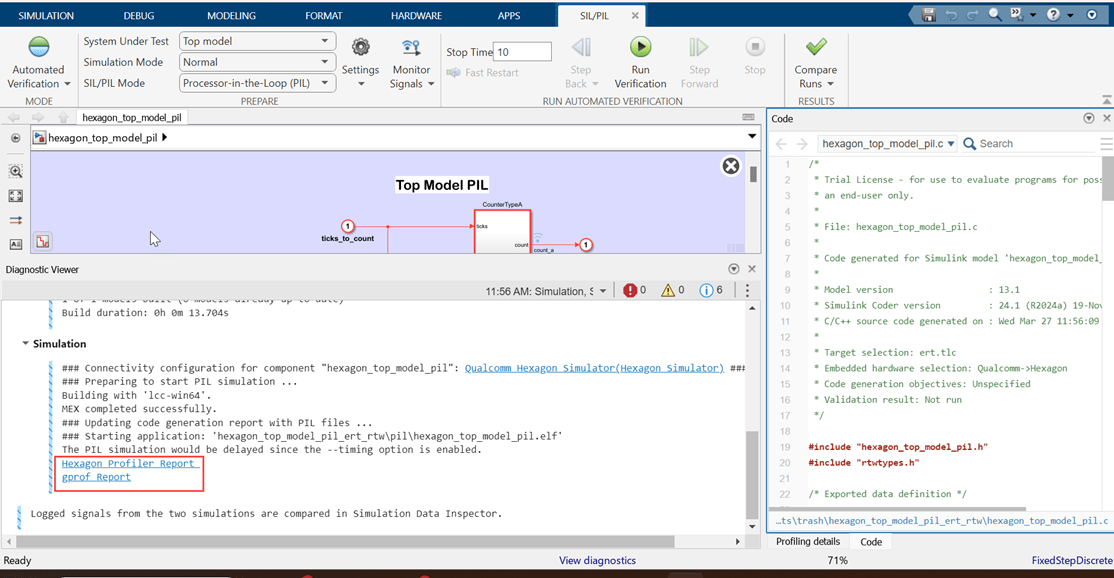

Go to Apps tab on the Simulink toolstrip and select SIL/PIL Manager.

From the SIL/PIL tab, click Run Verification to start the profiling-enabled verification.

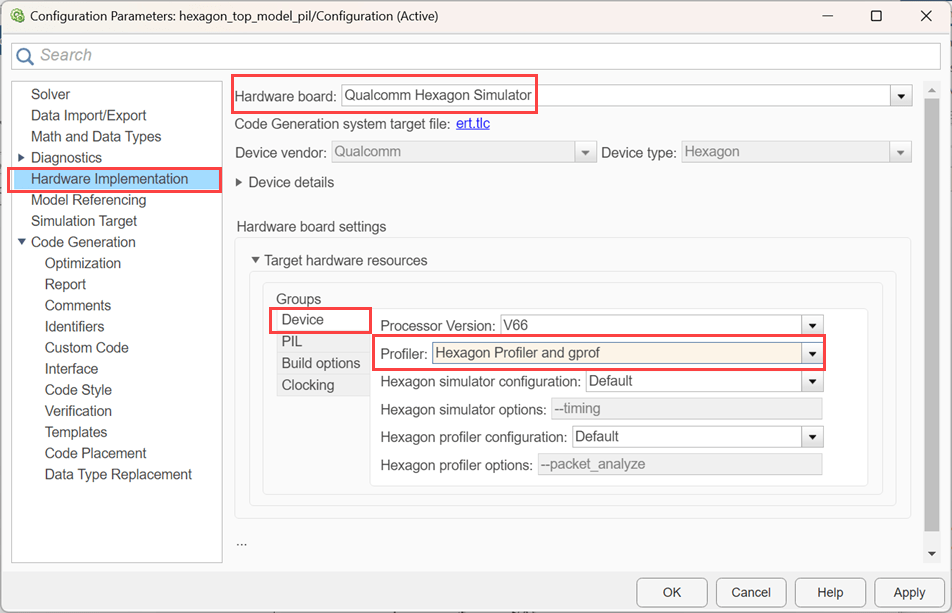

Once the simulation is completed, click on the Hexagon Profiler Report and gprof Report links to view the generated performance reports.

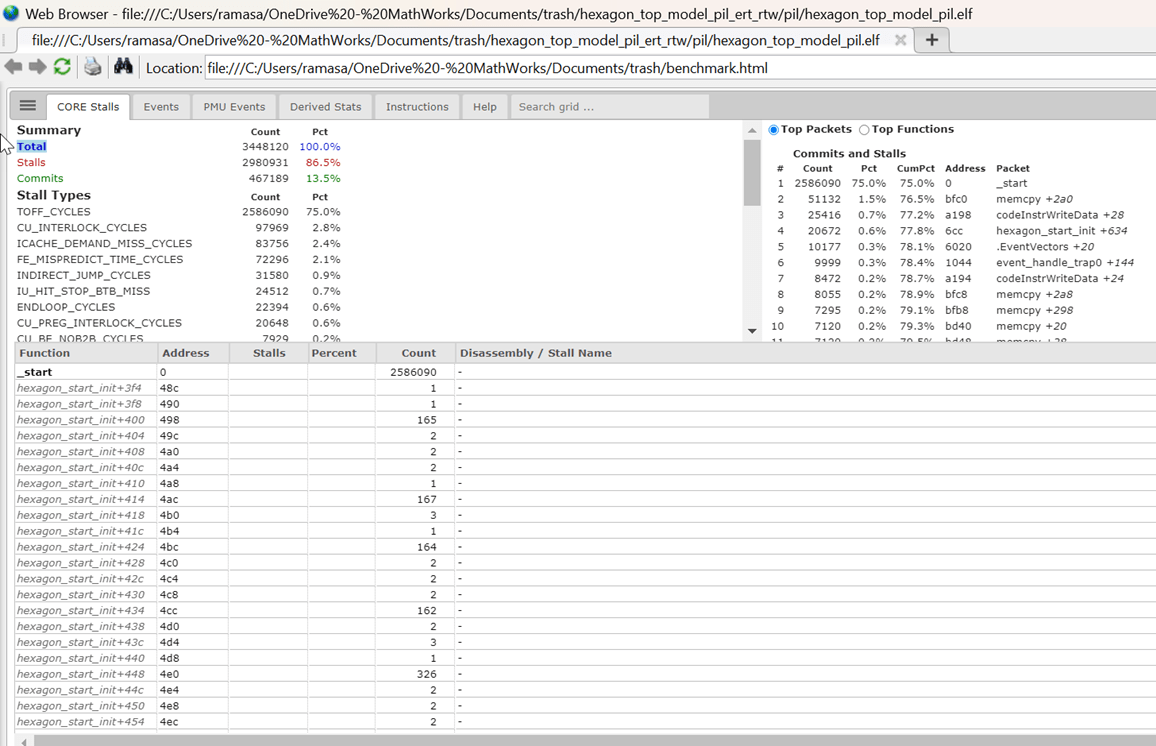

This image shows the generated Hexagon Profiler Report.

This image shows generated gprof report.