Divide by Constant HDL Optimized

将输入除以常量并舍入到整数并生成优化的 HDL 代码

库:

Fixed-Point Designer HDL Support /

Math Operations

描述

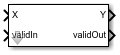

Divide by Constant HDL Optimized 模块使用具有周期精确延迟的 HDL 优化架构,输出输入除以一个常量的结果,并使用指定的舍入方法将结果舍入为整数。

Divide by Constant HDL Optimized 模块使用的算法在功能上类似于 Granlund-Montgomery-Warren 方法。除法运算是通过与倒数相乘计算的,这通常有助于在嵌入式系统上实现更好的性能。

端口

输入

输出

参数

提示

模块 Divide by Constant HDL Optimized、Real Divide HDL Optimized 和 Complex Divide HDL Optimized 都执行除法运算并生成优化的 HDL 代码。

Real Divide HDL Optimized 和 Complex Divide HDL Optimized 基于 CORIDC 算法。这些模块接受各种各样的输入,但会导致更大的延迟。

Divide by Constant HDL Optimized 只接受实数输入和常量除数。使用此模块会消耗 DSP 片,但会以更少的周期和更高的时钟频率完成除法运算。

算法

扩展功能

版本历史记录

在 R2021a 中推出