Generate an IP Core for Microchip SoC Platform from Simulink

Generate an IP Core

To generate a custom IP core to target the Microchip Polarfire® SoC Icicle Kit:

Open the HDL Workflow Advisor.

In the Set Target > Set Target Device and Synthesis Tool task, for Target workflow, select

IP Core Generation.For Target platform, select your hardware target from the drop-down list and click Run This Task:

Microchip Polarfire SoC Icicle kit

If you do not see your target hardware in the list, select Get more to download the target support package.

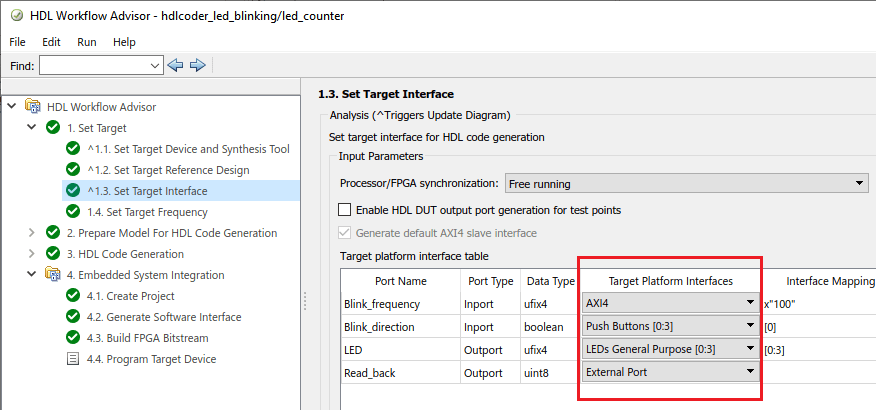

In the Set Target > Set Target Interface task, select a Target Platform Interface for each port, then click Apply.

You can map each DUT port to one of the following interfaces:

AXI4: Use this interface to connect to components that support burst data transmission. HDL Coder™ generates memory-mapped registers and allocates address offsets for the ports you map to this interface.External Port: Use the external ports to connect to FPGA external IO pins, or to other IP cores with external ports.To connect to FPGA external IO pins, for Bit Range / Address / FPGA Pin, enter a cell array of pin names. If you do not enter pin names in a cell array format, the external ports are left unconnected in the embedded system tool project. For example, you can enter:

{'Y10', 'A10', 'B10', 'D10'}.A board-specific interface, such as

LEDs General Purpose, orSwitches. Use these external ports to connect to external IO pins on the FPGA board.In the generated IP core, these ports are generic external ports. In a later step, if you use the HDL Workflow Advisor to integrate the generated IP core with embedded software in a Libero® project, the code generator connects these ports to the board-specific FPGA pins.

In the Generate RTL Code and IP Core task:

IP core folder: HDL Coder generates the IP core files in the output folder shown, including the HTML documentation.

IP repository: If you have an IP repository folder, enter its path manually or by using the Browse button. The coder copies the generated IP core into the IP repository folder.

Additional source files: If you are using a black box interface in your design to include existing Verilog® or VHDL® code, enter the file names. Enter each file name manually, separated with a semicolon (

;), or by using the Add button.Generate IP core report: Enable this option to generate HTML documentation for the IP core.

If you want to set options in the other HDL Workflow Advisor tasks, set them.

Right-click the Generate RTL Code and IP Core task and select Run to Selected Task.

To view the IP core report, click the link in the message window.

To learn more about custom IP core generation, see Custom IP Core Generation.

Requirements and Limitations for Custom IP Core Generation

To generate a custom IP core:

The DUT must be an atomic system.

If your target language is VHDL, the DUT cannot contain a model reference.

To map your DUT ports to an AXI4 interface:

Ports must have a bit width less than or equal to 32 bits.