Resource Sharing at Operator and Function Level to Optimize Area

Resource sharing is a design-wide optimization supported by HDL Coder™ for implementing area-efficient hardware. You can apply this optimization to share hardware resources at operator level or function level by identifying multiple functionally equivalent resources and replacing them with a single resource.

Resource Sharing at Operator Level

You can enable resource sharing of your MATLAB design by matching the bit widths of the operators used to perform calculations. Consider the MATLAB function div_noSharing, which performs two division operations, and the test bench div_noSharing_tb.

type("div_noSharing.m")% MATLAB Code

function [out1,out2] = div_noSharing(a,b,c,d)

out1 = a/b;

out2 = c/d;

end

type("div_noSharing_tb.m")% MATLAB Test Bench

% div_noSharing_tb

for i = 1:1000

a = randi(2000) + rand(1);

b = randi(2000) + rand(1);

c = randi(67000) + rand(1);

d = randi(67000) + rand(1);

[out,out1] = div_noSharing(a,b,c,d);

end

Generate HLS Code

To generate the HLS code run the div_run_me.m file.

div_run_me

===================================================

Design Name: div_noSharing

Test Bench Name: div_noSharing_tb

===================================================

Input types not specified for design(s) 'div_noSharing', inferring types by simulating the first test bench: 'div_noSharing_tb' in the base workspace.

============= Step1: Analyze Floating-Point Code ==============

Code generation successful.

============= Step1a: Verify Floating-Point Code ==============

### Analyzing the design 'div_noSharing'

### Analyzing the test bench(es) 'div_noSharing_tb'

### Begin Floating-Point Simulation (Instrumented)

### Floating-Point Simulation Completed in 2.4462 sec(s)

### Elapsed Time: 3.4092 sec(s)

============= Step2: Propose Types Based on Range Information ==============

============= Step3: Generate Fixed-Point Code ==============

### Generating Fixed-Point MATLAB Code div_noSharing_fixpt Using Proposed Types

### Generating Fixed-Point MATLAB Design Wrapper div_noSharing_wrapper_fixpt

### Generating Mex file for ' div_noSharing_wrapper_fixpt '

Code generation successful: View report

### Generating Type Proposal Report for 'div_noSharing' div_noSharing_report.html

===================================================

Code generation successful.

### Begin MATLAB to HLS Code Generation...

### Working on DUT: div_noSharing_fixpt.

### Using TestBench: div_noSharing_tb.

### Begin HLS Code Generation

### Generating Resource Utilization Report resource_report.html.

### Working on div_noSharing_fixptClass.hpp as div_noSharing_fixptClass.hpp.

### Working on div_noSharing_fixptModule.hpp as div_noSharing_fixptModule.hpp.

### Generating HLS Conformance Report div_noSharing_fixpt_hdl_conformance_report.html.

### HLS Conformance check complete with 0 errors, 0 warnings, and 0 messages.

### To rerun codegen evaluate the following commands...

---------------------

cgi = load('/tmp/Bdoc26a_3233028_1596266/tp6eeb0b87/hdlcoder-ex55318586/codegen/div_noSharing/hdlsrc/codegen_info.mat');

cfg = cgi.CodeGenInfo.codegenSettings;

fxpCfg = cgi.CodeGenInfo.fxpCfg;

codegen -float2fixed fxpCfg -config cfg -report

---------------------

### Code generation successful: View report

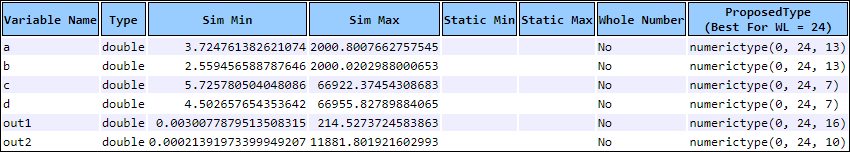

After converting from floating-point to fixed-point, the division operands have different bit widths. As a result, the outputs out1 and out2 of the two division operations also have different bit widths. Since the operands and outputs do not match in bit width, the HLS tool cannot share the divider hardware.

if (b == (sc_ufixed<24,11>)0.0) { varargout_1.range() = 576460752303423487; } else { sc_ufixed<48,24> div_temp; div_temp = (sc_ufixed<48,24,SC_TRN_ZERO>)((sc_ufixed<48,11>)a / b); varargout_1 = (sc_ufixed<59,35,SC_TRN_ZERO>)div_temp; } out1 = (sc_ufixed<24,9>)varargout_1; if (d == (sc_ufixed<24,17>)0.0) { b_varargout_1 = 1.677721599999994E+7; } else { sc_ufixed<48,24> b_div_temp; b_div_temp = (sc_ufixed<48,24,SC_TRN_ZERO>)((sc_ufixed<48,17>)c / d); b_varargout_1 = b_div_temp; } out2 = (sc_ufixed<24,9>)b_varargout_1; }

It creates two separate dividers, which increases resource usage on the hardware. You can see the Type Proposal Report by opening div_noSharing_report.html.

When the HLS tool synthesizes the generated HLS code, it cannot identify any sharing opportunity in the HLS code. This is because the two dividers cannot be shared, meaning the two division operations cannot be performed using single divider due to different bit-widths. Hence, it creates two dividers during synthesis. Therefore, the resource usage on the hardware is high.

Enable Resource Sharing by Matching Bit Widths

To enable resource sharing, you must match the bit widths of the division operands and outputs. You can do this by customizing the proposed types during the float-to-fixed conversion step in the HDL Workflow advisor. This ensures both divisions use operands and produce outputs with the same word length (WL) and fraction length (FL). For more information, see Fixed-Point Type Conversion and Refinement.

Alternatively, you can add the following type specifications to the fixpt configuration object at the command line.

fixptCfg.addTypeSpecification('div_noSharing', 'a', numerictype(0,30,13)); fixptCfg.addTypeSpecification('div_noSharing', 'b', numerictype(0,30,13)); fixptCfg.addTypeSpecification('div_noSharing', 'c', numerictype(0,30,13)); fixptCfg.addTypeSpecification('div_noSharing', 'd', numerictype(0,30,13)); fixptCfg.addTypeSpecification('div_noSharing', 'out1', numerictype(0,25,14)); fixptCfg.addTypeSpecification('div_noSharing', 'out2', numerictype(0,25,14)); codegen("-float2fixed","fixptCfg","-config","cfg",designName,"-launchreport");

===================================================

Design Name: div_noSharing

Test Bench Name: div_noSharing_tb

===================================================

Input types not specified for design(s) 'div_noSharing', inferring types by simulating the first test bench: 'div_noSharing_tb' in the base workspace.

============= Step1: Analyze Floating-Point Code ==============

============= Step1a: Verify Floating-Point Code ==============

### Analyzing the design 'div_noSharing'

### Analyzing the test bench(es) 'div_noSharing_tb'

### Begin Floating-Point Simulation (Instrumented)

### Floating-Point Simulation Completed in 2.5546 sec(s)

### Elapsed Time: 3.5621 sec(s)

============= Step2: Propose Types Based on Range Information ==============

============= Step3: Generate Fixed-Point Code ==============

### Generating Fixed-Point MATLAB Code div_noSharing_fixpt Using Proposed Types

### Generating Fixed-Point MATLAB Design Wrapper div_noSharing_wrapper_fixpt

### Generating Mex file for ' div_noSharing_wrapper_fixpt '

Code generation successful: View report

### Generating Type Proposal Report for 'div_noSharing' div_noSharing_report.html

===================================================

Code generation successful.

### Begin MATLAB to HLS Code Generation...

### Working on DUT: div_noSharing_fixpt.

### Using TestBench: div_noSharing_tb.

### Begin HLS Code Generation

### Generating Resource Utilization Report resource_report.html.

### Working on div_noSharing_fixptClass.hpp as div_noSharing_fixptClass.hpp.

### Working on div_noSharing_fixptModule.hpp as div_noSharing_fixptModule.hpp.

### Generating HLS Conformance Report div_noSharing_fixpt_hdl_conformance_report.html.

### HLS Conformance check complete with 0 errors, 0 warnings, and 0 messages.

### To rerun codegen evaluate the following commands...

---------------------

cgi = load('/tmp/Bdoc26a_3233028_1596266/tp6eeb0b87/hdlcoder-ex55318586/codegen/div_noSharing/hdlsrc/codegen_info.mat');

cfg = cgi.CodeGenInfo.codegenSettings;

fxpCfg = cgi.CodeGenInfo.fxpCfg;

codegen -float2fixed fxpCfg -config cfg -report

---------------------

### Code generation successful: View report

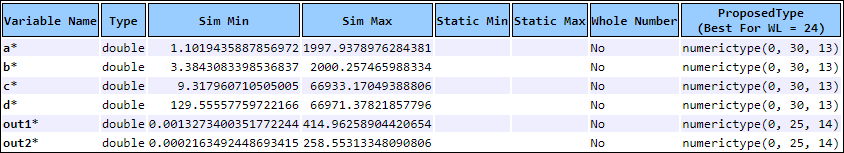

After making this modification, proposed fixed-point types in the Fixed-point conversion report appear as follows. Note that the customized fixed-point types are marked with asterisk.

During synthesis, the HLS tool identifies that both division operations are performed on similar operands. Hence, it synthesizes a single divider and shares it to perform two division operations on the hardware. This reduces hardware area without increasing latency.

Synthesis Results

By matching bit widths, you enable resource sharing and efficient hardware implementation. These synthesis results are obtained using Cadence Stratus HLS 24.02 with 45nm library and clock period of 5ns.

Metric | Without Resource Sharing | With Resource Sharing |

Total area | 25019.97 | 17697.75 |

Sequential area | 4602.64 | 3532.86 |

Combinational area | 20417.34 | 14164.89 |

Register bits | 815 | 629 |

Resource Sharing at Function Level

You can enable resource sharing across function calls in a MATLAB design by controlling function inlining during HLS code generation. Consider a MATLAB design mlhdlc_iir_filter.m which implements a cascaded IIR filter using the mlhdlc_iir_filter function. mlhdlc_iir_filter repeatedly calls a local function biquad_filter to process the signal through multiple filter sections. You can disable function inlining to share resources.

type("mlhdlc_iir_filter.m")function y = mlhdlc_iir_filter(x,sos,g)

% Copyright 2011-2015 The MathWorks, Inc.

% Declare persistent variables and initialize

numSections = numel(sos)/6;

persistent z

if isempty(z)

z = zeros(numSections, 2);

end

y = x;

for i=coder.unroll(1:numSections)

curSOS = sos((i-1)*6+1:i*6);

[y, z(i,:)] = biquad_filter(y,curSOS(1:3),curSOS(4:6),z(i, :));

end

y = y*g;

end

function [y,z] = biquad_filter(x,b,a,z)

% a(1) is assumed to be 1

% Direct-form II implementation

tmp = x - z(1)*a(2) - z(2)*a(3);

y = z(2) * b(3) + z(1) * b(2) + tmp * b(1);

z(2) = z(1);

z(1) = tmp;

end

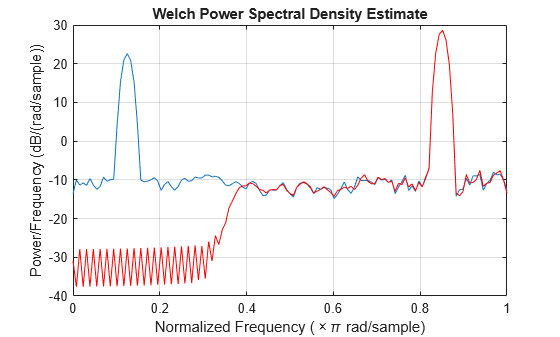

The test bench creates a noisy input signal, sets up the filter coefficients, and processes the signal sample by sample.

type("mlhdlc_iir_filter_tb.m")% Copyright 2011-2015 The MathWorks, Inc.

clear mlhdlc_iir_filter;

Fs = 800;

[z,p,k] = butter(15,300/Fs,'high');

[sos,g] = zp2sos(z,p,k); % Convert to SOS form

% Hd = dfilt.df2tsos(sos,g); % Create a dfilt object

% h = fvtool(Hd); % Plot magnitude response

% set(h,'Analysis','freq') % Display frequency response

L = 1000;

t = (0:L-1)'/Fs;

x = 5*sin(2*pi*50*t) + 10*cos(2*pi*340*t);

rng('default'); % always default to known state

x = x + .5*randn(size(x)); % noisy signal

y = zeros(size(x));

% Call to the design

sos = sos.';

for i=1:numel(x)

y(i) = mlhdlc_iir_filter(x(i), sos(:), g);

end

close all;

figure('Name', [mfilename, '_psd_plot']);

pwelch(x, 128);

hold on;

pwelch(y, 128);

yh = get(gca,'Children');

set(yh(1),'Color','r');

Generate HLS Code

When you generate HLS code, MATLAB inlines the biquad_filter function into mlhdlc_iir_filter. The HLS tool cannot identify the repeating logic, resulting in larger hardware area utilization. To generate the HLS code run the mlhdlc_iir_filter_runme.m file.

mlhdlc_iir_filter_runme

=================================================== Design Name: mlhdlc_iir_filter Test Bench Name: mlhdlc_iir_filter_tb =================================================== Input types not specified for design(s) 'mlhdlc_iir_filter', inferring types by simulating the first test bench: 'mlhdlc_iir_filter_tb' in the base workspace. ============= Step1: Analyze Floating-Point Code ============== Code generation successful. ============= Step1a: Verify Floating-Point Code ============== ### Analyzing the design 'mlhdlc_iir_filter' ### Analyzing the test bench(es) 'mlhdlc_iir_filter_tb' ### Begin Floating-Point Simulation (Instrumented) ### Floating-Point Simulation Completed in 4.9084 sec(s)

### Elapsed Time: 6.4455 sec(s)

============= Step2: Propose Types Based on Range Information ==============

============= Step3: Generate Fixed-Point Code ==============

### Generating Fixed-Point MATLAB Code mlhdlc_iir_filter_fixpt Using Proposed Types

### Generating Fixed-Point MATLAB Design Wrapper mlhdlc_iir_filter_wrapper_fixpt

### Generating Mex file for ' mlhdlc_iir_filter_wrapper_fixpt '

Code generation successful: View report

### Generating Type Proposal Report for 'mlhdlc_iir_filter' mlhdlc_iir_filter_report.html

===================================================

Code generation successful.

### Begin MATLAB to HLS Code Generation...

### Working on DUT: mlhdlc_iir_filter_fixpt.

### Using TestBench: mlhdlc_iir_filter_tb.

### Begin HLS Code Generation

### Generating Resource Utilization Report resource_report.html.

### Working on mlhdlc_iir_filter_fixptClass.hpp as mlhdlc_iir_filter_fixptClass.hpp.

### Working on mlhdlc_iir_filter_fixptModule.hpp as mlhdlc_iir_filter_fixptModule.hpp.

### Generating HLS Conformance Report mlhdlc_iir_filter_fixpt_hdl_conformance_report.html.

### HLS Conformance check complete with 0 errors, 0 warnings, and 0 messages.

### To rerun codegen evaluate the following commands...

---------------------

cgi = load('/tmp/Bdoc26a_3233028_1596266/tp6eeb0b87/hdlcoder-ex36706072/codegen/mlhdlc_iir_filter/hdlsrc/codegen_info.mat');

cfg = cgi.CodeGenInfo.codegenSettings;

fxpCfg = cgi.CodeGenInfo.fxpCfg;

codegen -float2fixed fxpCfg -config cfg -report

---------------------

### Code generation successful: View report

Enable Resource Sharing by Disabling Function Inlining

To allow the HLS tool to share hardware for repeated function calls, you need to prevent inlining by using coder.inline("never") pragma inside the biquad_filter function.

function [y,z] = biquad_filter(x,b,a,z) % a(1) is assumed to be 1 % Direct-form II implementation coder.inline("never"); tmp = x - z(1)*a(2) - z(2)*a(3); y = z(2) * b(3) + z(1) * b(2) + tmp * b(1); z(2) = z(1); z(1) = tmp; end

Alternatively, you can disable inlining for all functions by setting the HDL configuration option InstantiateFunctions to true. For more information, see Generate Instantiable Code for Functions.

hdlcfg = coder.config("hdl");

hdlcfg.InstantiateFunctions = true;The generated HLS code contains multiple calls to the same biquad_filter function. The HLS tool recognizes that these calls use identical logic and shares the hardware resources, reducing the total area.

Synthesis Results

By disabling inlining, you enable resource sharing and achieve an efficient hardware implementation. These synthesis results are obtained using Cadence Stratus HLS 24.02 with 45nm library and clock period of 5ns.

Metric | With Inlining | Without Inlining (Resource Sharing) |

Total area | 16806.98 | 1796.40 |

Sequential area | 7080.77 | 585.50 |

Combinational area | 9726.21 | 1210.90 |

Register bits | 1294 | 107 |