Auto-Generated Memory Map with Individual Address Option

This example highlights the use of the auto-generated memory map with individual address option when you generate a SystemC™/TLM component from a Simulink® model using the tlmgenerator target for either Simulink Coder™ or Embedded Coder®.

In Simulink, each component input or output is bound point-to-point to another component. In SystemC/TLM, each component communicates through a TLM socket. This socket handles all the incoming and outgoing communication formatted inside TLM transactions. Because each system handles communication differently, we must define a communication interface for the SystemC/TLM component when it is generated from a Simulink model. Depending on the intended use of this SystemC/TLM component, this communication interface could require building a memory map (or address) for each input/output in the component. This memory map may be simple or detailed.

The auto-generated memory map with individual address option generates a TLM component with one read register per model output and write register per model input with individual addresses. Each Simulink model input is bound to its corresponding write register and each output is bound to its corresponding read register. When created with this option, the generated TLM component could be used in a virtual platform (VP) as a standalone component in a test bench or it could be attached to a communication channel.

For this example we use a Simulink model of a FIR filter as the basis of the SystemC/TLM generation.

Requirements to run this example:

SystemC 2.3.1 (includes the TLM library)

Note: The example includes a code generation build procedure. Simulink does not permit you to build programs in the MATLAB® installation area. If necessary, change to a working directory that is not in the MATLAB installation area prior to starting any build.

1. Open the Preconfigured Model

To open the FIR Filter model with auto-generated memory map with individual address, click the Open Model button.

The following model opens in Simulink.

open_system('tlmgdemo_aimem');

2. Set the Option to Auto-Generated Memory Map with Individual Address

In the Configuration Parameters dialog box, select the TLM Generation view in the left-hand pane. In the TLM Mapping tab, under Socket Mapping, select One combined TLM socket for input data, output data and control. Under Combined TLM Socket, select Auto-generated memory map and Individual input and output address offsets, as shown in the following image.

3. Set the Other Options

Set the remaining TLM Generation options and click OK to apply these settings and exit the Configuration Parameters dialog box.

4. Build the Model

To build the model, execute the following command in the MATLAB command window:

slbuild('tlmgdemo_aimem/DualFilter');

### Searching for referenced models in model 'DualFilter'. ### Total of 1 models to build. ### Starting Simulink Coder build procedure for model: DualFilter ### Successful completion of Simulink Coder build procedure for model: DualFilter Build Summary Top model targets: Model Build Reason Status Build Duration ================================================================================================ DualFilter Information cache folder or artifacts were missing. Code generated. 0h 0m 11.875s 1 of 1 models built (0 models already up to date) Build duration: 0h 0m 13.576s

5. Open the Generated Files

Open the following files in the MATLAB Editor:

6. Observe the Generated Code

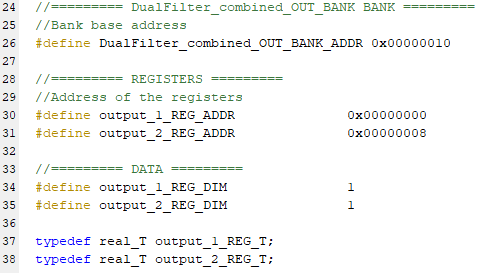

Find the following lines of code. These lines represent the input and output definitions of the FIR Filter when generated as a TLM component with individual address memory map.

To provide a set of input to the generated TLM component, an TLM initiator should send two write TLM transactions:

one with a payload containing a data of type input_1_REG_T at the address DualFilter_combined_IN_BANK_ADDR + input_1_REG_ADDR.

one with a payload containing a data of type input_2_REG_T at the address DualFilter_combined_IN_BANK_ADDR + input_2_REG_ADDR.

To obtain a set of output from the generated TLM component, an TLM initiator should send three read TLM transactions:

one with a payload containing a data of type output_1_REG_T at the address DualFilter_combined_OUT_BANK_ADDR + output_1_REG_ADDR.

one with a payload containing a data of type output_2_REG_T at the address DualFilter_combined_OUT_BANK_ADDR + output_2_REG_ADDR.