HDL Verifier

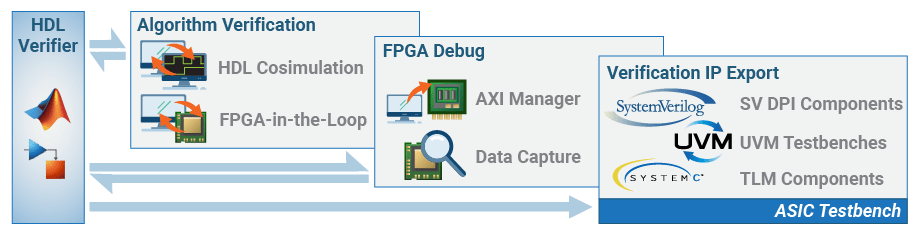

HDL Verifier™ enables you to reuse your system-level design environment in your HDL design environment. You can test and verify RTL designs against golden reference models in MATLAB® and Simulink®, debug designs in simulators or hardware, and generate testbenches and verification IP.

With HDL Verifier, you can verify FPGA, ASIC, and SoC designs using testbenches that run in MATLAB and Simulink with RTL designs that run in your HDL simulator. You can reuse these testbenches with AMD®, Altera®, and Microchip FPGA development boards to verify hardware implementations and probe internal signals to debug designs. You can also generate Universal Verification Methodology (UVM) components from MATLAB and Simulink for use in your SystemVerilog verification environment. All these capabilities are compatible with existing HDL code and code generated by HDL Coder™.

Get Started

Learn the basics of HDL Verifier

Algorithm Verification

Execute MATLAB or Simulink in sync with FPGA or HDL simulation

FPGA Debug

Debug hardware designs by connecting an FPGA board to MATLAB or Simulink

Export of Verification IP

Generate testbenches for ASIC and advanced FPGA designs

Verification of Generated HDL Code

Generate testbenches to verify HDL code generated with HDL Coder

HDL Verifier Supported Hardware

Support for third-party hardware, such as AMD, Intel®, and Microchip FPGA and SoC devices