Considerations for DPI Component Generation with MATLAB

You can export a MATLAB® function as a component with a direct programming interface (DPI) for use in a SystemVerilog simulation. HDL Verifier™ wraps generated C code with a DPI wrapper that communicates with a SystemVerilog thin interface function in a SystemVerilog simulation.

For MATLAB, you generate the component using the dpigen function.

Note

This feature requires a MATLAB Coder™ license and the ASIC Testbench for HDL Verifier add-on

Supported MATLAB Data Types

Supported MATLAB data types are converted to SystemVerilog data types, as shown in this

table. Use the svdpiConfiguration object to configure the dpigen function, and set the PortsDataType

property to Compatible C type, Logic vector,

or Bit vector data types.

Generated SystemVerilog Types

| MATLAB | SystemVerilog | ||

|---|---|---|---|

| Compatible C Type | Logic Vector | Bit Vector | |

uint8 | byte unsigned | logic [7:0] | bit [7:0] |

uint16 | shortint unsigned | logic [15:0] | bit [15:0] |

uint32 | int unsigned | logic [31:0] | bit [31:0] |

uint64 | longint unsigned | logic [63:0] | bit [63:0] |

int8 | byte | logic signed [7:0] | bit signed [7:0] |

int16 | shortint | logic signed [15:0] | bit signed [15:0] |

int32 | int | logic signed [31:0] | bit signed [31:0] |

int64 | longint | logic signed [63:0] | bit signed [63:0] |

logical | byte unsigned | logic [0:0] | bit [0:0] |

fi (fixed-point data type) | Depends on the fixed-point word length. If the fixed-point word length is greater than the host word size (for example, 64-bit vs. 32-bit), then this data type cannot be converted to a SystemVerilog data type by MATLAB Coder and you will get an error. If the fixed-point word length is less than or equal to the host word size, MATLAB Coder converts the fixed-point data type to a built-in C type. |

The logic vector length ( |

The bit vector length ( |

single | shortreal | ||

double | real | ||

complex | The coder flattens complex signals into real and imaginary parts in the SystemVerilog component. | ||

| vectors, matrices | arrays For example, a 4-by-2 matrix in MATLAB is converted into a one-dimensional array of eight elements in SystemVerilog. By default, the coder flattens matrices in column-major order. To change to row-major order, use the | ||

structure | The coder flattens structure elements into separate ports in the SystemVerilog component. | ||

| enumerated data types | enum | ||

Generated Shared Library

Function dpigen automatically compiles the shared library

needed to run the exported DPI component in the SystemVerilog environment. The

makefile that builds the shared library has the extension

_rtw.mk. For example, for fun.m, the make file

name is fun_rtw.mk.

During compilation, the function dpigen generates a library

file.

Windows® 64:

function_win64.dllLinux®:

function.so

function is the name of the MATLAB function you generated the DPI component from.

Note

If you use 64-bit MATLAB on Windows, you get a 64-bit DLL, which can be used only with a 64-bit HDL simulator.

Make sure that your MATLAB version matches your HDL simulator version.

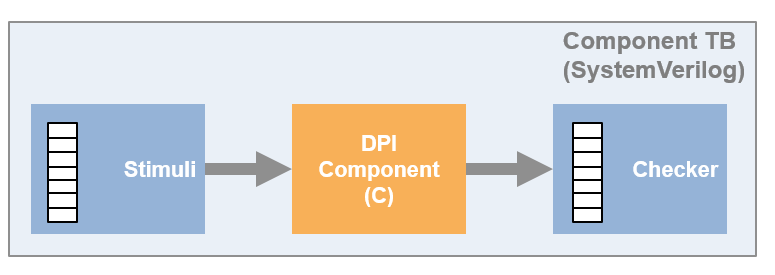

Generated Testbench

Function dpigen also creates a testbench. You can use this

testbench to verify that the generated SystemVerilog component is functionally

equivalent to the original MATLAB function. The generator runs your MATLAB code to save input and output data vectors for use in the testbench.

This testbench is not intended as a replacement for a system testbench for your own

application. However, you can use the generated testbench as a starting example when

creating your own system testbench.

Generated Outputs

C and header files from your algorithm, generated by MATLAB Coder

C and header files for the DPI wrapper, generated by HDL Verifier

SystemVerilog file that exposes the component and adds control signals

SystemVerilog package file that contains all the function declarations of the DPI component

SystemVerilog testbench (with the

-testbenchoption)Data files used with the HDL simulator (with the

-testbenchoption)HDL simulator scripts, such as

*.door*.sh(with the-testbenchoption)Makefile

*.mk

Generated SystemVerilog Wrapper

Generated Control Signals

SystemVerilog code generated for a sequential function by function

dpigen contains a set of control signals.

clk: synchronization clockclk_enable: clock enablereset: asynchronous reset

When generating SystemVerilog for a combinational design, the generated code

does not have the above control signals. Specify sequential or combinational by

using the ComponentKind argument of the svdpiConfiguration object.

Generated Initialize Function

All SystemVerilog code generated by the dpigen function

includes an Initialize function. The

Initialize function is called at the beginning of the

simulation.

For example:

import "DPI" function void DPI_Subsystem_initialize();

If the asynchronous reset signal is high (goes from 0 to 1),

Initialize is called again.

Simulation Considerations

When simulating the DPI component in your HDL environment,

reset, clock, and

clk_enable behave as follows:

When

clk_enableis0, the DPI output function is not executed, and the output values are not updated.When

clk_enableis1andresetis0, the DPI output function is executed on the positive edge of the clock signal.When

resetis1, the internal state of the DPI component is set to its initial value. This action is equivalent to using theclearfunction in MATLAB to update persistent variables. Then output values reflect the DPI component initial state and current input values. For more details on persistent variables, see Persistent Variables.

Limitations

Large fixed-point numbers that exceed the system word length are not supported.

Some optimizations, such as constant folding, are not supported because they change the interface of the generated C function. For more information, see MATLAB Coder Optimizations in Generated Code (MATLAB Coder).

HDL Verifier limits matrices and vectors to one-dimensional arrays in SystemVerilog. For example, a 4-by-2 matrix in MATLAB is converted to a one-dimensional array of eight elements in SystemVerilog.

The

PostCodegencallback in configuration objects is not supported.You cannot set up third-party tools in MATLAB Online™, so you cannot use these features in MATLAB Online:

Testbench execution for DPI generation

Use of EDA toolchains for compiling DPI shared libraries