JTAG AXI Manager

Integrate and configure AXI manager over a JTAG connection. To use JTAG AXI manager, you must first include the AXI Manager intellectual property (IP) in your AMD® Vivado® project.

AXI Manager IP

The AXI Manager IP acts as a bridge that translates data between an AXI peripheral and MATLAB® or Simulink® software. This IP connects to your application IP over a JTAG connection.

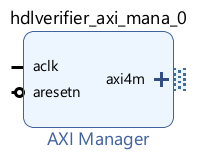

This block diagram shows the interface of the AXI Manager IP.

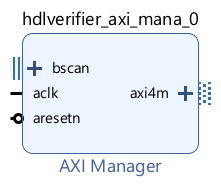

This block diagram shows the interface of the AXI Manager IP for the AMD Versal® devices.

AXI Manager IP Ports

The interface of the AXI Manager IP includes the ports described in these tables.

| Port | Description |

|---|---|

| bscan (Versal only) | BSCAN interface to connect to CIPS IP. |

| axi4m | AXI4-full manager interface. |

| Port | Direction | Description |

|---|---|---|

| aclk | Input | Clock signal for AXI4-full interface. |

| aresetn | Input | Active-low reset. Reset signal for AXI4-full interface. |

AXI Manager IP Connections for Versal Devices

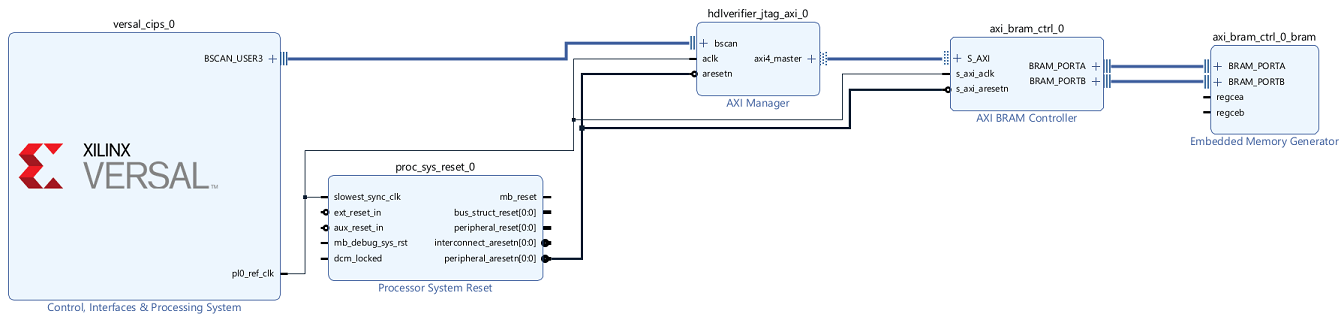

For an AMD Versal device, connect the AXI Manager IP to the BSCAN_USER3 interface of the AMD Versal platform CIPS IP, as this figure shows.

To enable the BSCAN_USER3 interface, enable the PL BSCAN2 interface in the CIPS IP. For more information about the CIPS IP, see Control Interfaces and Processing System LogiCORE IP Product Guide on the AMD website.

AXI Manager IP Parameters

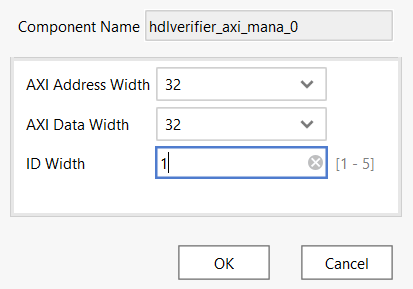

After you include the AXI Manager IP in your design, open the block.

Configure these parameters:

AXI Address Width — Address bus width in bits. The IP supports 32, 40, or 64 bits.

AXI Data Width — Data bus width in bits. The IP supports 32 or 64 bits.

ID Width — ID width in bits. The value of this parameter must match the ID width of the AXI4 subordinate.

When the program is running on your FPGA board, you can communicate with the

AXI Manager IP by creating an aximanager object. To access the

subordinate memory locations on the board, use the readmemory and writememory object

functions.

See Also

aximanager | readmemory | writememory