SystemVerilog and UVM Templates

Generate a unified verification methodology (UVM) component or a SystemVerilog DPI

component from a MATLAB® function. Use the new svdpiConfiguration object to specify the template to use for code

generation. You can also set the properties of the object to override the default values

in the template-variables. Then, use the dpigen function to generate your component.

Select a built-in template for common component kinds, or create your own custom template. For an example that uses this template engine, see Use Templates to Create SystemVerilog DPI and UVM Components.

Note

This feature requires the ASIC Testbench for HDL Verifier add-on.

General-Purpose Templates

HDL Verifier™ provides the following built-in templates:

Combinational module — This template captures the inputs and outputs of a MATLAB function. Use it to create a combinational SystemVerilog module, with no clock or reset ports.

It includes these variables:

Override by setting properties in the

svdpiConfigurationobject.ComponentTypeNameTestBenchTypeName

Override by setting the

TemplateDictionaryproperty.ComponentPackageTypeName

Sequential module — This template captures the inputs and outputs of a MATLAB function. It also adds ports for clock, clock enable, and reset signals. Use it when you have state in your function (such as persistent variables) to create a sequential, registered SystemVerilog module. For more information about persistent variables, see Persistent Variables.

The sequential module template includes these variables:

Override by setting properties in the

svdpiConfigurationobject.ComponentTypeNameTestBenchTypeName

Override by setting the

TemplateDictionaryproperty.ComponentPackageTypeName

Sequential module with variable-size outputs — This template is functionally the same as the sequential module template, but it has accommodations for variable-size ports. Use this template if one or more of the inputs or outputs to your function is defined as a variable-size vector. This template creates a SystemVerilog module with the respective port as a SystemVerilog open array ([ ]). This code shows the generated interface for a function named

foo, declaringin1andyas variable-size ports.module foo_dpi( input bit clk, input bit clk_enable, input bit reset, input real in1 [], output shortint y [] );

This template includes these variables:

Override by setting properties in the

svdpiConfigurationobject.ComponentTypeNameTestBenchTypeName

Override by setting the

TemplateDictionaryproperty.ComponentPackageTypeName

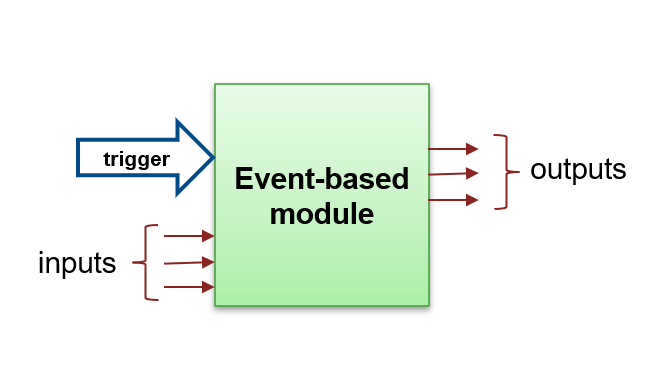

Event-based module — This template provides a module interface with data input and output ports, but without any clock, clock enable, or reset ports. You can trigger the module behaviors using events from outside the module. Use this template to synchronize between processes in your system.

Available triggers are:

DPI_INITDPI_RESETDPI_OUTPUTDPI_UPDATEDPI_TERMINATE

You can trigger events from your SystemVerilog environment by using the SystemVerilog operator

->in your testbench. For an example, see Generate Event-Based SystemVerilog DPI Component.Note

This template excludes testbench generation.

This template includes these variables:

Override by setting properties in the

svdpiConfigurationobject.ComponentTypeName

Override by setting the

TemplateDictionaryproperty.ComponentPackageTypeName

SystemVerilog class — This template packages the Simulink® behavior in a SystemVerilog class. You can instantiate this class in your HDL verification environment and call its methods to reproduce the Simulink behavior. For an example, see Generate SystemVerilog Class for DPI Component.

Note

This template excludes testbench generation.

This template includes these variables:

Override by setting properties in the

svdpiConfigurationobject.ComponentTypeName

Override by setting the

TemplateDictionaryproperty.ComponentPackageTypeName

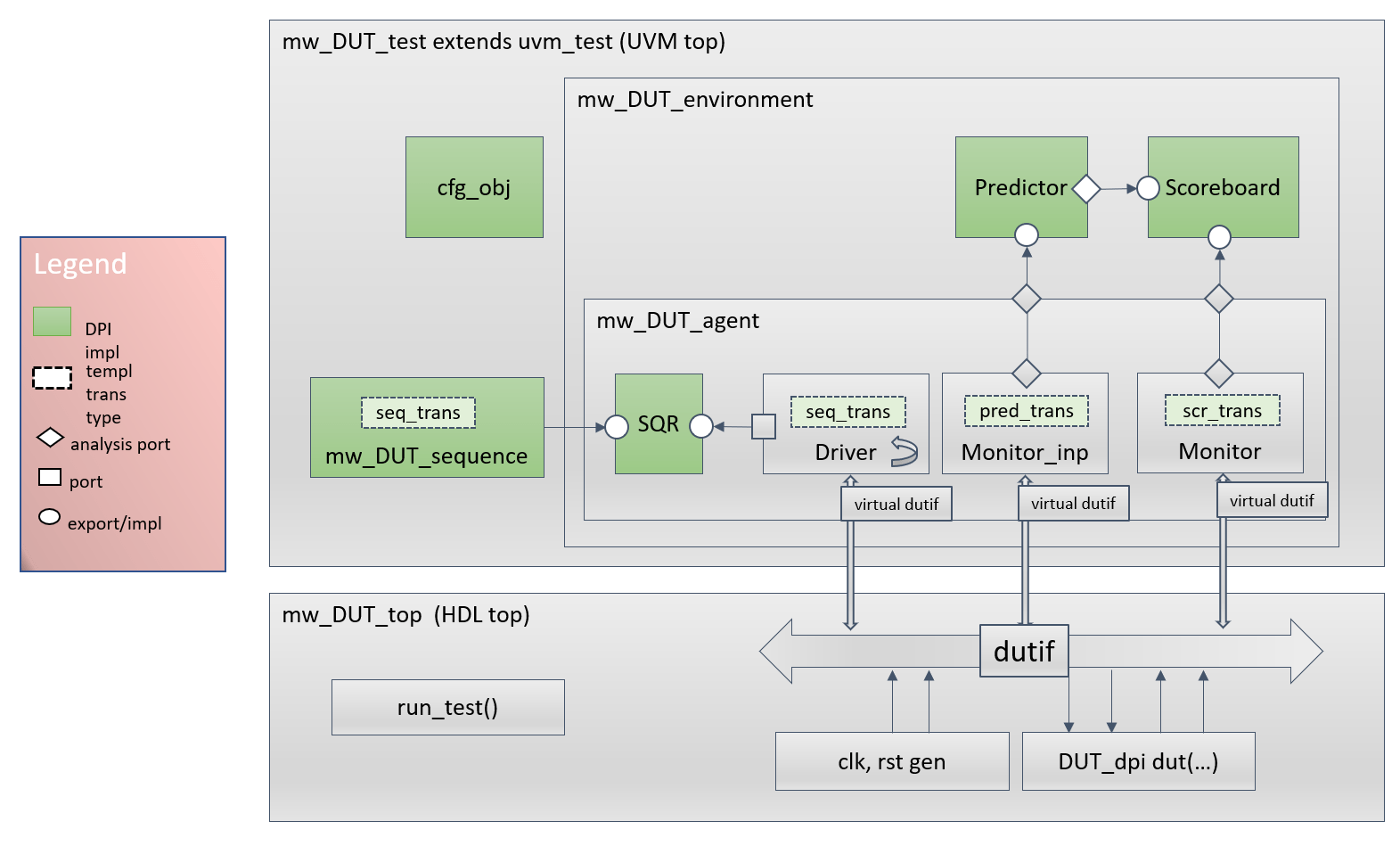

UVM Templates

These templates generate UVM components from MATLAB functions, which you can integrate into a full UVM testbench. This image shows the UVM testbench structure. You can generate the parts highlighted in green by using the UVM templates.

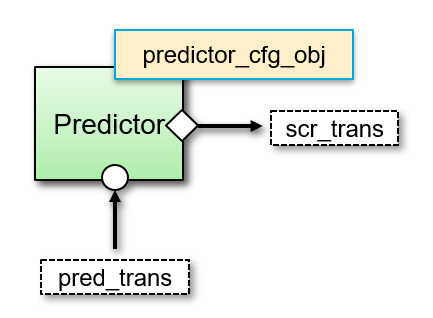

Predictor component — This template generates a UVM predictor module. The module has an export that inputs a predictor transaction and an analysis port that outputs a scoreboard transaction.

The predictor template includes these variables:

Override by setting properties in the

svdpiConfigurationobject.ComponentTypeNameTestBenchTypeName

Override by setting the

TemplateDictionaryproperty.ComponentPackageTypeNameInputTransTypeNameOutputTransTypeName

You can optionally map ports to port groups by using the

addPortGroupobject function.PREDICTOR_INPUTSCONFIG_OBJECT_INPUTS

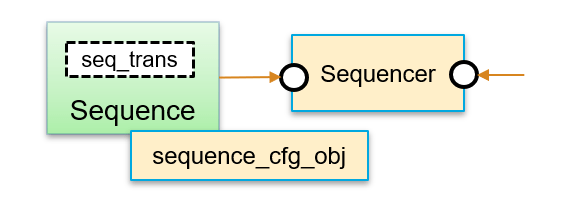

Sequence component — This template generates a UVM sequence module. The module has an export that inputs a predictor transaction and an analysis port that outputs a scoreboard transaction.

The sequence template includes these variables:

Override by setting properties in the

svdpiConfigurationobject.ComponentTypeNameTestBenchTypeName

Override by setting the

TemplateDictionaryproperty.ComponentPackageTypeNameSequenceTransTypeNameSequencerTypeNameSequenceCountSequenceFlushCount

You can optionally map ports to port groups by using the

addPortGroupobject function.SEQUENCE_INPUTSCONFIG_OBJECT_INPUTS

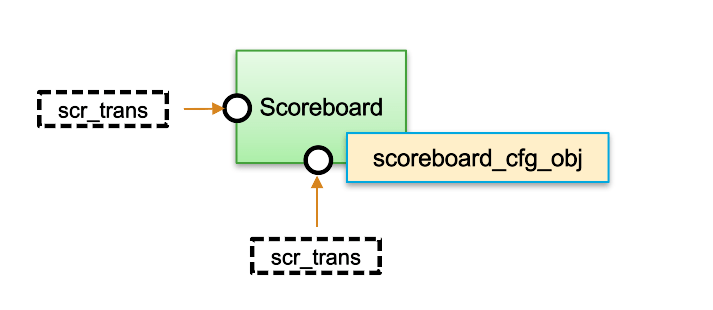

Scoreboard component — This template generates a UVM scoreboard module and a scoreboard configuration object. The module has two exports that input a scoreboard transaction.

The scoreboard template includes these variables:

Override by setting properties in the

svdpiConfigurationobject.ComponentTypeNameTestBenchTypeName

Override by setting the

TemplateDictionaryproperty.ComponentPackageTypeNameInputTransTypeNameOutputTransTypeNameConfigObjTypeName

Map ports to port groups by using the

addPortGroupobject function.PREDICTOR_INPUTSMONITOR_INPUTSCONFIG_OBJECT_INPUTS

Testbench Templates

The dpigen function uses the testbench

templates when it is invoked with the -testbench argument. The

dpigen function simulates the MATLAB function and logs the inputs and outputs. The

dpigen function then generates a SystemVerilog testbench

module that instantiates the generated SystemVerilog component (DUT), drives the

logged inputs to the DUT, and compares the DUT outputs against the logged outputs

from the MATLAB simulation. This option assures that the generated SystemVerilog

module is equivalent to the original MATLAB function.

The following built-in testbench templates are available:

Combinational testbench

Sequential testbench

Sequential testbench with variable size outputs

Predictor testbench

Sequence testbench

Scoreboard testbench