Generate Structured Text Code for Hierarchical Simulink Subsystem with Virtual Subsystems

This example shows how to generate structured text code for a hierarchical subsystem that contains a virtual subsystem. Use virtual hierarchical subsystems when:

The model is relatively small and does not require multiple subsystems.

You need code modularity and reusability in the same model.

You want to keep all subsystem files and folders in the same model file for easier management.

The simulation performance is a concern and you need to optimize the model for simulation speed.

You need improved portability. You can use virtual subsystems in different models without the need for additional file management, which makes it easier to create a library of reusable subsystems.

To see an example of a hierarchical subsystem that simplifies a large, complex model, see Generate Structured Text Code for Hierarchical Simulink Subsystems.

Open Example Model

Open the example model.

mdl = "plcdemo_hierarchical_virtual_subsystem.slx";

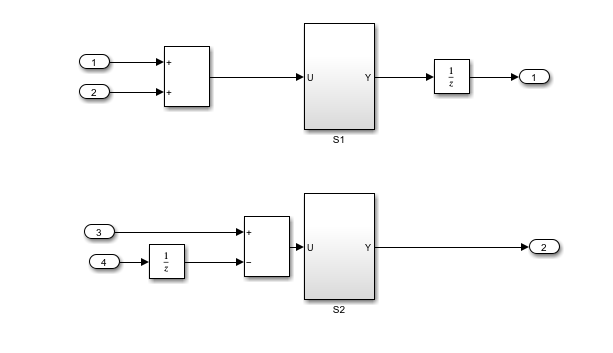

open_system(mdl)The model contains a top-level subsystem called HierarchicalSubsystem. Under the top-level subsystem are two subsystems, S1 and S2, that operate on the top-level subsystem inputs at every time step.

Generate and Inspect PLC Code

To generate structured text code:

In the Apps tab, click PLC Coder.

In the PLC Code tab, click Settings > PLC Code Generation Settings. Change the Target IDE to

3S CoDeSys 2.3. Click OK.Select the

HierarchicalSubsystemblock. In the PLC Code tab, click Generate PLC Code.

Alternatively, to generate structured text code from the MATLAB® command line, use the plcgeneratecode function.

generatedFiles = plcgeneratecode('plcdemo_hierarchical_subsystem_virtual/HierarchicalSubsystem');

Inspect Generated Code

Because the subsystems S1 and S2 are not marked as atomic subsystems they are not generated as separate function blocks. In this case all the code is generated under the top-level subsystem, which allows users to easily reuse the subsystem or replace the code with their own code.

type("plcsrc\plcdemo_hierarchical_virtual_subsystem.exp")

FUNCTION_BLOCK HierarchicalSubsystem

VAR_INPUT

ssMethodType: SINT;

In1: LREAL;

In2: LREAL;

In3: UINT;

In4: LREAL;

END_VAR

VAR_OUTPUT

Out1: LREAL;

Out2: LREAL;

END_VAR

VAR

UnitDelay_DSTATE_i: LREAL;

UnitDelay1_DSTATE: LREAL;

UnitDelay_DSTATE: LREAL;

UnitDelay_DSTATE_a: LREAL;

END_VAR

VAR_TEMP

rtb_Gain_n: LREAL;

END_VAR

CASE ssMethodType OF

SS_INITIALIZE:

(* SystemInitialize for Atomic SubSystem: '<Root>/HierarchicalSubsystem' *)

(* InitializeConditions for UnitDelay: '<S1>/Unit Delay1' *)

UnitDelay1_DSTATE := 0.0;

(* InitializeConditions for UnitDelay: '<S3>/Unit Delay' *)

UnitDelay_DSTATE := 0.0;

(* InitializeConditions for UnitDelay: '<S2>/Unit Delay' *)

UnitDelay_DSTATE_a := 0.0;

(* InitializeConditions for UnitDelay: '<S1>/Unit Delay' *)

UnitDelay_DSTATE_i := 0.0;

(* End of SystemInitialize for SubSystem: '<Root>/HierarchicalSubsystem' *)

SS_STEP:

(* Outputs for Atomic SubSystem: '<Root>/HierarchicalSubsystem' *)

(* Gain: '<S3>/Gain' incorporates:

* Sum: '<S1>/Sum1'

* Sum: '<S3>/Sum'

* UnitDelay: '<S1>/Unit Delay1'

* UnitDelay: '<S3>/Unit Delay' *)

Out2 := ((UINT_TO_LREAL(In3) - UnitDelay1_DSTATE) - UnitDelay_DSTATE) * 0.75;

(* Gain: '<S2>/Gain' incorporates:

* Sum: '<S1>/Sum'

* Sum: '<S2>/Sum'

* UnitDelay: '<S2>/Unit Delay' *)

rtb_Gain_n := ((In1 + In2) - UnitDelay_DSTATE_a) * 0.5;

(* Outport: '<Root>/Out1' incorporates:

* UnitDelay: '<S1>/Unit Delay' *)

Out1 := UnitDelay_DSTATE_i;

(* Update for UnitDelay: '<S1>/Unit Delay1' *)

UnitDelay1_DSTATE := In4;

(* Update for UnitDelay: '<S3>/Unit Delay' *)

UnitDelay_DSTATE := Out2;

(* Update for UnitDelay: '<S2>/Unit Delay' *)

UnitDelay_DSTATE_a := rtb_Gain_n;

(* Update for UnitDelay: '<S1>/Unit Delay' *)

UnitDelay_DSTATE_i := rtb_Gain_n;

(* End of Outputs for SubSystem: '<Root>/HierarchicalSubsystem' *)

END_CASE;

END_FUNCTION_BLOCK