Trade Determinism and Data Integrity to Improve System Performance

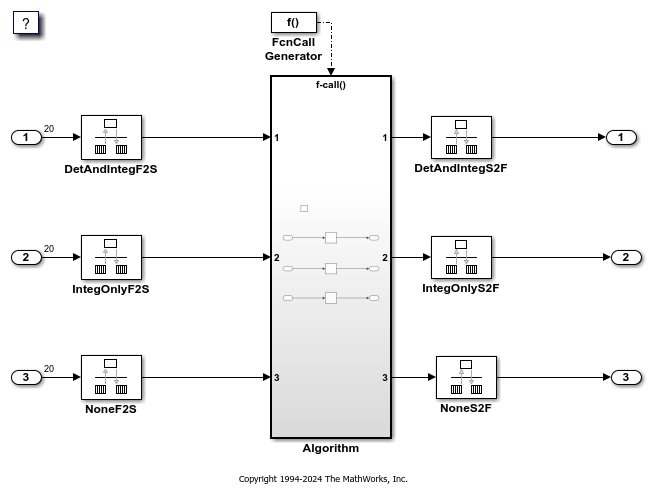

This model shows the differences in the operation modes of the Rate Transition block when used in a multirate, multitasking model. The flexible options for the Rate Transition block allow you to select the mode that is best suited for your application. You can trade levels of determinism and data integrity to improve system performance.

Rate Transition Block Modes of Operation

Ensure data integrity and determinism (DetAndInteg): Data is transferred such that all data bytes for the signal (including all elements of a wide signal) are from the same time step. Additionally, it is ensured that the relative sample time (delay) from which the data is transferred from one rate to another is always the same. Only ANSI® C code is used, no target specific 'critical section' protection is needed.

Ensure integrity (IntegOnly): Data is transferred such that all data bytes for the signal (including all elements of a wide signal) are from the same time step. However, from one transfer of data to the next, the relative sample time (delay) for which the data is transferred can vary. In this mode, the code to read/write the data is run more often than in the DetandInt mode. In the worst case, the delay is equivalent to the DetandInt mode, but the delay can be less which is important in some applications. Also, this mode supports data transfers to/from asynchronous rates which the DetandInt mode cannot support. Only ANSI-C code is used, no target specific 'critical section' protection is needed.

No data consistency operations are performed (None): For this case, the Rate Transition block does not generate code. This mode is acceptable in some applications where atomic access of scalar data types is guaranteed and when the relative temporal values of the data are not important. This mode does not introduce any delay.

Data Transfer Assumptions

Basis of operation for data transfers between tasks:

Data transitions occur between a single reading task and a single writing task.

A read or write of a byte sized variable is atomic.

When two tasks interact through a data transition, only one of them can preempt the other.

For periodic tasks, the faster rate task has higher priority than the slower rate task; the faster rate task always preempts the slower rate task.

All tasks run on a single processor. Time slicing is not allowed.

Processes do not crash/restart (especially while data is being transferred between tasks).

Model MultirateMultitaskingRateTransitions

open_system('MultirateMultitaskingRateTransitions')

Model MultirateMultitaskingRateTransitions shows the differences in the operation modes of the following Rate Transition blocks.

Rate Transition Block DetAndIntegF2S

Determinism and data integrity (fast to slow transition):

The block output is used as a persistent data buffer.

Data is written to output at slower rate but done during the faster rate context.

Data as seen by the slower rate is always the value when both the faster and slower rate last executed. Any subsequent steps by the faster rate (and associated data updates) while the slower rate is running are not seen by the slower rate.

Rate Transition Block DetAndIntegS2F

Determinism and data integrity (slow to fast transition):

Uses two persistent data buffers, an internal buffer and the blocks output.

The internal buffer is copied to the output at the slower rate but done during the faster rate context.

The internal buffer is written at the slower rate and during the slower rate context.

The data that Fast rate sees is always delayed, i.e. data is from the previous step of the slow rate code.

Rate Transition Block IntegOnlyF2S

Data integrity only (fast to slow transition):

The block output is used as a persistent data buffer.

Data is written to buffer during the faster rate context if a flag indicates it not in the process of being read.

The flag is set and data is copied from the buffer to output at the slow rate, the flag is then cleared. This is an additional copy as compared to the deterministic case.

Data as seen by the slower rate can be from a more recent step of the faster rate than from when the slower rate and faster rate both executed.

Rate Transition Block IntegOnlyS2F

Data integrity only (slow to fast transition):

Uses two persistent data buffers, both are internal buffers.

One of the 2 buffers is always copied to the output at faster rate.

One of the 2 buffers is written at the slower rate and during the slower rate context, then the active buffer is switched.

The data as seen by the faster rate can be more recent than for the deterministic case. Specifically, when both the slower and faster rate have their hits, the faster rate will see a previous value from the slower rate. But, subsequent steps for the faster rate may see an updated value (when the slower rate updates the non-active buffer and switches the active buffer flag.

Rate Transition Block NoneF2S

No code is generated for the Rate Transition block when determinism and data integrity is waived.

Rate Transition Block NoneS2F

No code is generated for the Rate Transition block when determinism and data integrity is waived.

bdclose('MultirateMultitaskingRateTransitions');