MIPI D-PHY Parallel Link Compliance Kit

Test the compliance to the MIPI D-PHY specification with respect to clock-to-data timing in the forward direction and waveform quality in the reverse transmission using Parallel Link Designer.

This kit can be used for testing compliance with respect to the clock-to-data timing in the forward direction (Controller to Peripheral). The reverse transmission (Peripheral to Controller) operates at ¼ the data rate of the forward transmission. The specification is vague on timing requirements for these transfers and expects the logic implementation of the Controller to train itself during the synchronous calibration mode to ensure timing is met for reverse transmission. Thus this kit is configured to test waveform quality only for reverse transmission. Lastly, this kit does not include any LP mode functionality.

Open MIPI D-PHY Kit

Open the MIPI D-PHY kit in the Parallel Link Designer app using the openSignalIntegrityKit function.

openSignalIntegrityKit("MIPI_D_PHY_PLD_Kit");

Kit Overview

Project name: MIPI_D_PHY_PLD_Kit

Interface name: MIPI_D_Phy

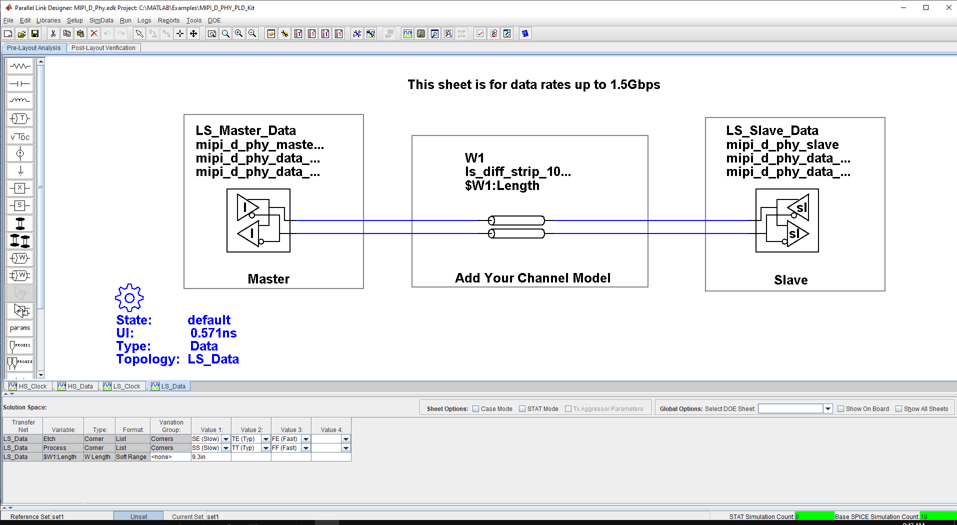

The MIPI D-PHY kit defines schematic sheets for high speed data rates above 1.5 Gb/s and low speed data rates less than or equal to 1.5 Gb/s. The kit can be simulated with either IsSPICE (the default) or HSPICE.

For more information about the MIPI D-PHY channel compliance schematics, transfer net properties, and compliance rules, refer to the document MIPI_D_Phy_PLD_Kit.pdf located inside the kit project directory.

References

[1] MIPI D-PHY Specification. mipi_D-PHY_specification_v1-2.pdf. Rev. 1.2.