Post-Layout Verification of Parallel Link

Post-layout verification provides you with an integrated signal integrity and timing environment to verify system-level SI and timing margins for your fully or partially routed PCB design databases.

The post-layout process supports single-board and multiboard analysis, along with connectivity through packages, connectors, and cabling. The post-layout verification environment provides you the ability to extract and analyze PCB databases from any combination of the following CAD (Computer Aided Design) formats:

ODB++™

Cadence® Allegro

Cadence APB

Intercept Pantheon

Altium® Designer

Altium P-CAD

IBIS EBD

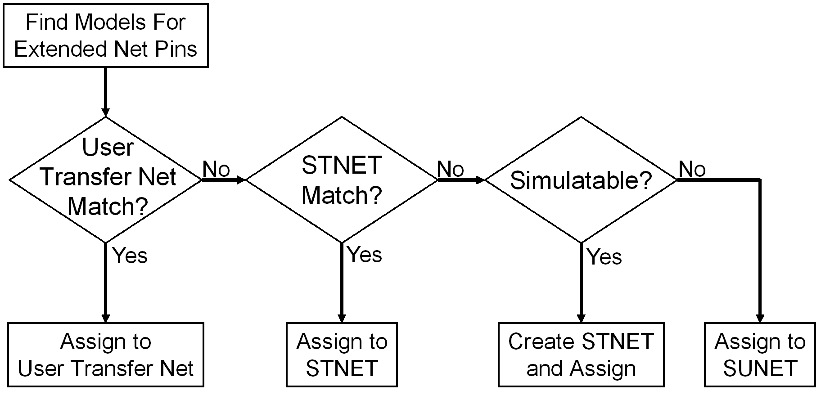

Post-layout analysis takes place in the interface of a serial link design project. If the interface you are working in has pre-layout transfer nets defined, post-layout uses them from the reference schematic set. If there are no transfer nets in the reference schematic set of the interface, the Parallel Link Designer app creates sheets with system transfer nets (STNETs).

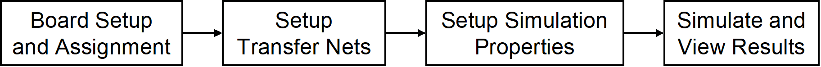

The post-layout verification workflow is the same for each PCB database type. First import the PCB databases, setup the boards, connect the instances if there are multiple boards in the system, run assignment, setup and analyze the nets, set up simulation properties, then simulate and view the results.

Board

The first step in the post-layout verification process is board set-up and assignment. A PCB database you import to the Parallel Link Designer app is called a board. At the board level, check and edit all stackups, voltage nets, and models. To create variations of a PCB database using different stackups, voltages, or models, create multiple boards with unique names.

To perform the setup and assignment functions, access the Post-Layout Setup & Assignment dialog box from the Setup > Setup & Assignment menu in the app toolstrip.

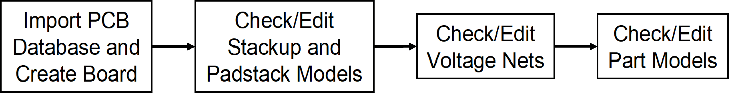

For each board in the system, specify the type of the PCB database and the files in the database, view or edit the stackup, view or set voltage nets, and manage models by clicking the Import & Setup Board button in the Post-Layout Setup & Assignment dialog box. The Import & Setup Board dialog box has four tabs:

Import

Use the Import Board tab to import a PCB database and create a board. Select the PCB database type from the PCB Database Type selector list. By default, the Parallel Link Designer app creates an instance for each board and copies the PCB database files into the current project. If you do not copy the PCB database into the project, you cannot re-import the database files.

Stackup

The Stackup tab shows the stackup from the PCB database and allows control of padstack models. The Stackup Editor on the left side of the tab shows the stackup as it is read in from the PCB database. If necessary, you can override the auto-generated trace models using the editor. The right side of the tab has controls for the auto-generated padstack backdrill options, differential extraction, and DRC control.. For more information, see Stackup and Extraction Control in Parallel Link Project.

Voltages

The Voltages tab shows the CAD nets in the PCB database for the board and allows you to specify the voltage for specific voltage nets. Non-voltage nets have an NA value in the voltage column.

Note

The Voltages tab does not control the voltages in the IBIS or SPICE models for TX/RX designators. This tab is mainly used to correctly define the on-board terminations that require connection to a specific voltage.

Parts

Use the Parts tab to match models to parts in the PCB database.

Instance

An instance is an internal copy of a board that you can connect to other instances and analyze. Every board that is used in the design has at least one instance. If you use the same board more than once, you must define a separate instance for each use. For example, a system consisting of a motherboard with two DIMM slots that has the same type of DIMM plugged into each slot will have one instance of the motherboard and two instances of the DIMM.

Connection

A Connection is a pin-to-pin path from the pins of a reference designator on one instance to the pins of a reference designator on a second instance. In a multi-board system, connections between instances are specified in the Connections pane of the Post-Layout Setup & Assignment dialog box. To add a connection, click the Add Connection button.

Assignment

The Assignment process is an automated process for associating nets in the PCB database with transfer nets. This simplifies the setup of the essential net properties in the typical scenarios that you will face:

Interface without Transfer Nets

If you did not do a pre-layout analysis in an interface, you can create and edit transfer nets from the post-layout interface. When you set the properties of a transfer net, you set the properties of all nets assigned to that transfer net. For example, when you change the properties of a transfer net, the app automatically assigns those properties to all nets in a data bus.

Interface with Transfer Nets from Pre-Layout Analysis

If you completed pre-layout analysis in an interface, the app automatically assigns the nets you created in post-layout analysis to the transfer nets you created in the pre-layout analysis.

Design Kits

A design kit is an interface with models and preconfigured transfer nets. The app automatically assigns the nets you created in post-layout analysis to these transfer nets.

In all cases, the transfer nets and the assignment process ensure that all nets in an interface are set up and ready to simulate in a fraction of the time needed to set up each net in the interface individually.

Population

Populations allow you to setup multiple configurations of a system for simulation in one project. The app handles populations through the naming of instances.

For example, if a one-slot motherboard can accept one of three DIMMs (dual in-line memory modules), it can be set up by creating three instances of the motherboard and one instance of each DIMM. In this case, three populations can be defined: the motherboard with RCA installed, the motherboard with RCB installed and the motherboard with RCC installed

Simulation

Before you run a simulation, you must select the nets for the post-layout verification. Select the nets and add them to the list of nets to simulate. You also need to set up the stimulus patterns from simulation properties.

Topology

Extended nets that can be simulated (assigned to an STNET or user transfer nets) can have topologies created from the extracted PCB data. View these topologies from the Pre-Layout Analysis tab. The topologies are useful for understanding how an actual network is routed and to resolve waveform quality or timing issues identified by using post-layout verification. Once the extracted post-layout networks are in the pre-layout analysis environment, you can perform quick “what-if” analyses to identify an appropriate solution.