RLDRAM III Architectural Kit

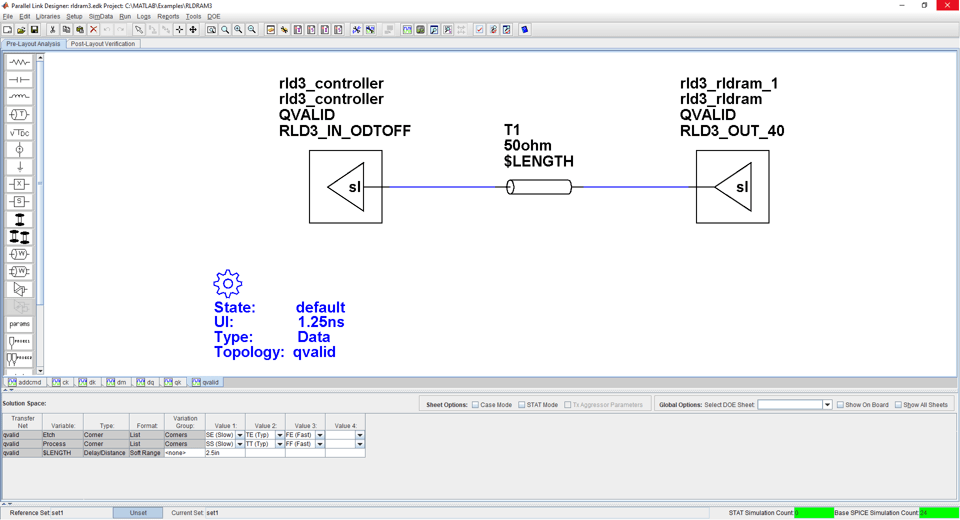

Implement a RLDRAM III interface for pre-layout analysis or post-layout verification.

This RLDRAM III architectural signal integrity kit includes all transfer nets, timing models, waveform processing levels and generic models for a RLDRAM III interface. This includes generic buffer models for the controller and RLDRAM along with fully functional timing models and complete waveform processing levels. You can modify the kit to match your exact implementation. Then, perform complete pre-layout solution space analysis and/or full post-layout verification for waveform quality and timing margins.

Open RLDRAM III Kit

Open the RLDRAM III kit in the Parallel Link Designer app using the openSignalIntegrityKit function.

openSignalIntegrityKit("RLDRAM3");

Kit Overview

For more information about the RLDRAM III architectural signal integrity kit, including block diagrams, system configurations, transfer nets and libraries, along with instructions on how to customize the kit for a specific implementation, refer to the document RLDRAM3.pdf that is attached to this example as a supporting file.

References

[1] Micron – 576Mb: x18, x36 RLDRAM3 Features (Advance datasheet). 576_rldram3.pdf – Rev. B 1/12 EN.

[2] Micron – TN-44-01: Technical Note, RLDRAM3 Design Guide. TN_44_01_RLDRAM_3_Design_Guide.fm – Rev. A 8/11 EN.