STAT Mode

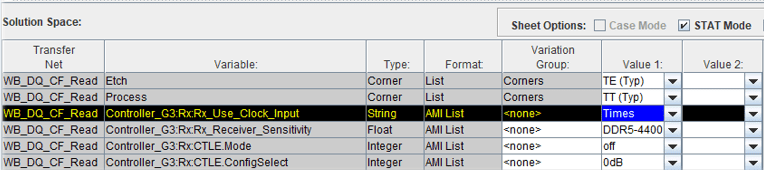

STAT Mode is a simulation mode that uses a statistical engine to perform network characterization, statistical analysis, and time domain simulations. This simulation methodology is derived from the IBIS-AMI specification for performing high speed channel simulations with IBIS-AMI models. The simulation engine used in STAT mode is a derivative of the Serial Link Designer app and makes simulation with IBIS-AMI models possible in the Parallel Link Designer app. You must enable the STAT mode on each sheet in the Sheet Options for the AMI parameters to show up in the solution space.

When analysis runs in STAT Mode, a SPICE step simulation runs to get the step response of the net. In IBIS AMI terms, this is the analog channel step response. You can use STAT mode to simulate any type of buffer models (IBIS or SPICE) to analyze the response and performance of the network. This simulation uses the analog model from the IBIS file. It does not use the SI analog model equivalent circuit parameters. The ODT (on die termination) settings are part of the IBIS analog model and included in the step response. The step response is processed to create the analog channel impulse response that forms the basis for the channel simulation.

The channel simulation produces statistical and time domain analysis results. The statistical engine uses the transfer function to determine the statistical eye along with a bit error ratio (BER) and other data. Statistical engine bases the analysis on an LTI (Linear Time Invariant) network assumption along with LTI equalization (if supported by the model).

Time Domain Analysis uses the same network characterization results as statistical analysis along with a bit sequence to derive the output waveform, persistent eye, BER estimate, and other data. The persistent eye is the amplitude statistics accumulated from a specific time domain waveform. It is accumulated by triggering an ideal recovered clock in exactly the same way that you accumulate an eye diagram in a modern digital sampling scope. Unlike statistical analysis time domain analysis is a bit-by-bit simulation that analyzes the network with any non-LTI behavior.

When waveform analysis is specified, the time domain waveform is post-processed to produce the same results as a non-STAT Mode simulation. This includes waveform overshoot and waveform quality checks as well as etch delays for timing analysis. The number of bits processed is a subset of the entire waveform and is specified by the simulation parameter Waveform Analysis Bits.