Transfer Nets in Parallel Link Designer

In a parallel link project, an interface contains a collection of signals such as clock, data, or strobes. These signals implement the physical layer protocol from the core of one IC to the core of another IC. Each signal is called a transfer net. They consist of the drivers, receivers, electrical conductors and passive components involved in transmitting that signal type.

Transfer nets are the primary net-class data structure in the Parallel Link Designer app. They are common to both pre-layout and post-layout analysis. You can re-use the transfer nets in multiple ways from one phase of a project to another, or between projects.

Transfer Net Properties

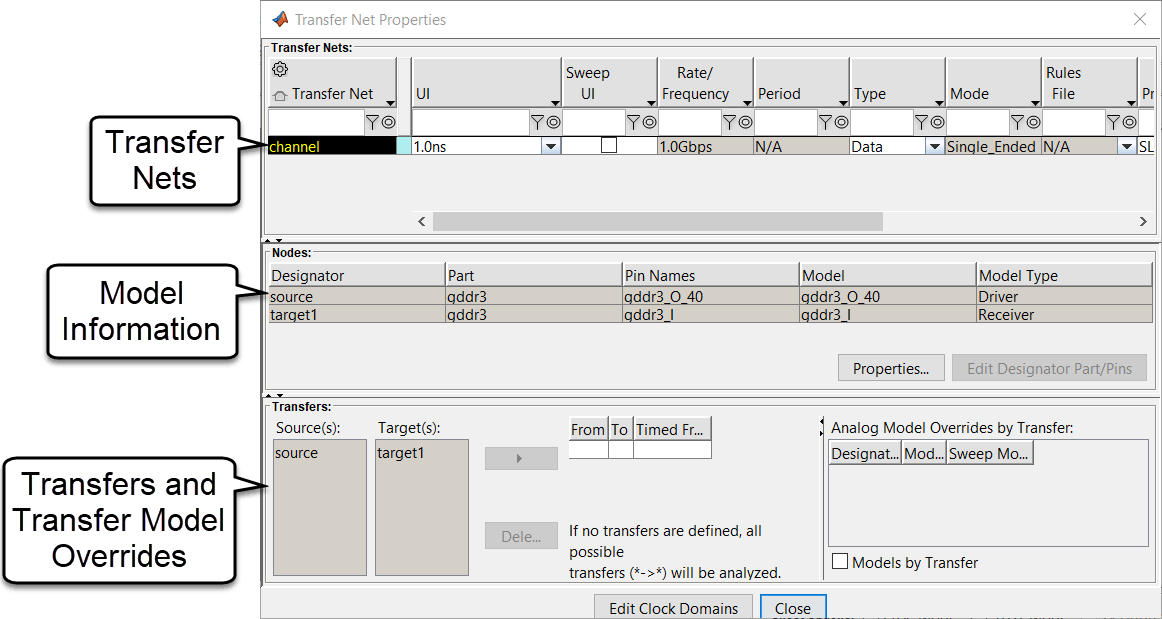

To edit the transfer net properties, launch the Transfer Net Properties dialog box from Setup > TNet Properties.

The dialog box contains:

list of all transfer nets in the current schematic set with their properties,

list of the model information for the selected transfer nets, and

transfers and transfer model overrides for selected transfer nets.

Transfer Nets

These are the basic properties for each transfer nets. They are listed in the Transfer Nets Properties dialog box.

| Column | Description |

|---|---|

| Transfer Net | The name of the transfer net. This is the same as the schematic sheet name in the pre-layout. |

| UI | The UI for the transfer net. The clock domain file contains the name and value of the UI. |

| Sweep UI | Sweep the UI for the transfer net. |

| Rate/Frequency | The Rate/Frequency is derived from the UI depending on the Type for the transfer net. For transfer nets of Type

For transfer nets of

Type

|

| Period | The period of the waveform is derived from the UI depending on the Type for the transfer net For transfer

nets of Type

For transfer nets of Type

|

| Type | The Type defines the default stimulus

pattern used for simulation and Waveform Analysis and

Timing Analysis. The Type can

be either |

| Mode | The Mode is either

|

| Rules File | Any rules files contained in the library. You can view the mask data for the selected rules file in the results table of the Signal Integrity Viewer app when viewing the analysis results. |

| Source Probe Points | The Source Probe Points control the probe points used in Waveform Analysis. The transfer net setting can be overridden for specific models through extensions in the IBIS file. |

| Target Probe Points | The Target Probe Points control the probe points used in Waveform Analysis. The transfer net setting can be overridden for specific models through extensions in the IBIS file. Note In STAT Mode the Target Probe Point is always pad.

|

| Jitter | The Jitter applies to transfer nets with

Type values |

| Timed Edge | The Timed Edge specifies which simulation

edges are to be used inTiming Analysis. The

Timed Edge can be either If If An alternative way to time to a specific edge would be to allow this keyword to be its default value (both) and the specify the setup and hold definitions in the timing file to ignore one of the edges. An example would be: SETHLD data *to R clk Rset Fset Rhold Fhold Rset/Rhold or Fset/Fhold

are set to NA. |

Nodes

The Nodes section of the dialog contains a table with one row per designator.

| Column | Description |

|---|---|

| Designator Name | The name of the designator. |

| Part | The MathWorks Part name for this designator. |

| Pin Names | The names of the pins included in the designator. The pin names are from the IBIS component and IBIS file specified by the MathWorks Part. |

| Model | The default IBIS model for the designator. It is determined from the

precedence in the IBIS specification using the Pin entries and

Model Selector if present. |

| Model Type | The model type from the IBIS Model_Type parameter in the default IBIS model. |

Transfers

If a schematic sheet has multiple I/O buffers, transfers tell the Parallel Link Designer app how many simulations to create, one with each of the I/O buffers driving. When analyzing the waveforms, the app checks timing and signal integrity at each of the receiving designators for each case.

To define a transfer, in the Transfer Net Properties dialog box, select a transmitter in the Source(s) parameter, select a receiver in the Target(s) parameter, and click the arrow button to create a new row. If no transfers are defined, all possible transfers will be analyzed.

Analog Model Overrides by Transfer

To enable analog model overrides, select the Models by Transfer option. For each transfer specified in the Transfers segment of the Transfer Net Properties dialog the model to be used for each designator can be specified. The Analog Model Overrides by Transfer table contains one row for each designator on the net. When a transfer is selected in the Transfers table, the Analog Model Overrides by Transfer table can be used to specify a model other than the default model. The list next to each designator contains the models that can be selected for that designator. The list is created in the following way:

If the model of a designator is a model selector in the IBIS file, all models in the model selector are listed.

If the model of a designator is not a model selector in the IBIS file:

Only look at models in the same IBIS component as the designator's model

If transfer net is differential, only look at differential models (models that are referenced in the diff pin section).

If transfer net is single-ended, only look at single-ended models (models that are not referenced in the diff pin section).

If designator is target in transfer: get all input, I/O models.

If designator is source in transfer: get all output, I/O models.

If designator is not in transfer and is output, allow output, I/O.

If designator is not in transfer and is input, allow input, I/O.

If designator is not in transfer and is I/O, allow input, output, I/O models in part.

Using Timed From Column

The classic source synchronous transfer is comprised of a data net and a clock net, both nets having a driver on the source device and a receiver on the target device. Another method that achieves similar improved timing margins consists of a single clock net that goes to input clock pins on both the source and target devices. Instead of a DELAY_SKEW between the source device data pin and the source device clock output pin, there is a DELAY_SKEW between the source device data pin and source clock input pin. This special case is handled in the clock transfer net by specifying a transfer from the source clock output pin to the target clock input pin. Then, it is specified that the timing for this transfer net is performed from the source clock input pin to the target clock input pin putting the source clock input pin in the Timed From column of the Transfers section.

Transfer Net in Pre-Layout Analysis

In pre-layout analysis, the Parallel Link Designer app defines each transfer net on a separate schematic sheet and simulates in a separate simulation run. You can parameterize the circuit element values in a transfer net schematic. This allows you to evaluate many variations without changing the schematic. A widebus transfer net schematic can also contain crosstalk interferers..

Transfer Net in Post-Layout Analysis

In post-layout analysis, each net on a PCB is called a CAD net. You can combine the CAD nets with drivers, receivers, packages, discrete components, and connector pins to form an extended net. An extended net contains designators, and reaches from one IC to another. Extended nets can also traverse multiple PCBs. You can identify individual extended nets and assign them to transfer nets for all major PCB flows.