Generate HDL Code for FPGA Platforms from Simscape Models

If you have HDL Coder™ and Simscape™, you can generate HDL code from your models to deploy onto FPGA platforms. The advisor converts your Simscape model into a Simulink® implementation model that HDL Coder uses to generate HDL code.

Converting your Simscape model to HDL code allows you to:

Take advantage of the Simscape physical system modeling capabilities.

Rapidly prototype models using the reconfigurability and parallelism capabilities of the FPGA.

Simulate the HDL implementation in real time with hardware-in-the-loop (HIL).

Before you run the Simscape HDL Workflow Advisor, configure your network to exclude delays and enabled runtime parameters. To learn more about the capabilities and limitations of Simscape models in HDL Coder, visit Get Started with Simscape Hardware-in-the-Loop Workflow (HDL Coder).

Generate HDL Code by Using the Simscape HDL Workflow Advisor

This example shows you how to convert a Simscape model to HDL code using the Simscape HDL Workflow Advisor.

To open a Simscape model that is ready for HDL code generation, enter:

openExample('simscape_shared/FullWaveBridgeRectifierForSimscapeHDLAdvisorExample')Generate baseline results for comparison.

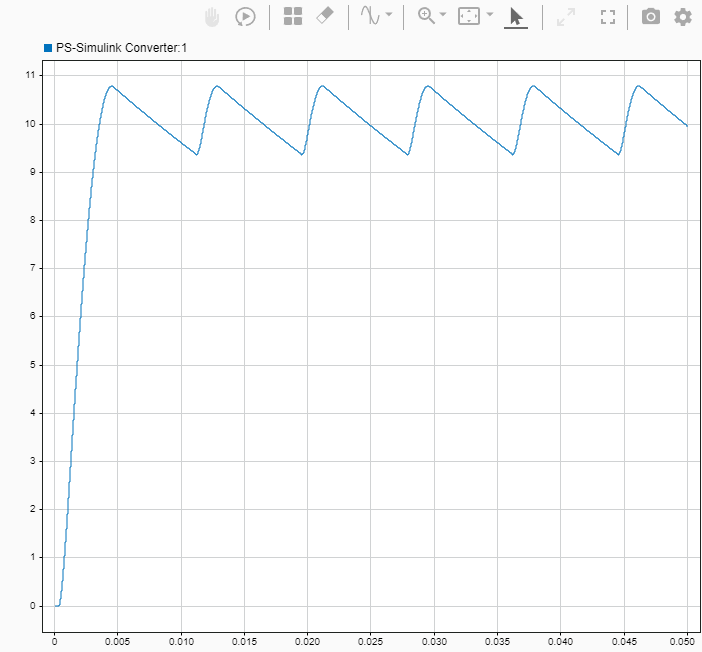

baselineModel = "FullWaveBridgeRectifierForSimscapeHDLAdvisor"; sim(baselineModel) runIDs = Simulink.sdi.getAllRunIDs; runID = runIDs(end); run = Simulink.sdi.getRun(runID); signal1 = run.getSignalByIndex(1); signal1.checked = true; Simulink.sdi.view

The baseline simulation returns the expected results for the full-wave bridge rectifier load voltage.

Run the Simscape HDL Workflow Advisor for the model.

sschdladvisor(baselineModel)

Click the Run All to run all the steps in the advisor. Wait for the implementation model to generate. The advisor gives tips to improve model robustness for HDL code generation.

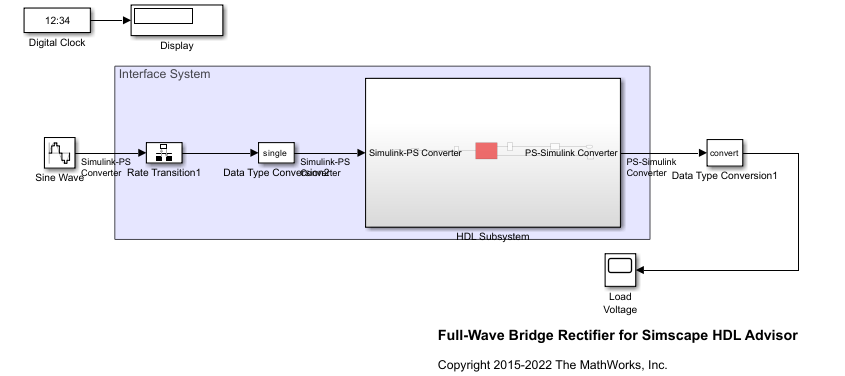

When the Simscape HDL Workflow Advisor generates the implementation model, the advisor reports that the task passed and displays a link to the generated implementation model,

gmStateSpaceHDL_FullWaveBridgeRectifierForS.Open the generated implementation model by clicking the link.

The model contains blocks from the original model and new blocks that support the HDL Workflow Advisor:

Digital Clock, Display, Sine Wave, and Load Voltage — Control the original model functionality.

Rate Transition1— Handles the transfer of data between blocks that operate at different rates.Data Type Conversion1,Data Type Conversion2— Convert between double and single precision data types. HDL code generation requires single-precision data.HDL Subsystem— Contains an HDL code generation-compatible version of your Simscape network.Load Voltage Scope block — Displays the load voltage.

Save the model name as a workspace variable.

HDLmodelname = 'gmStateSpaceHDL_FullWaveBridgeRectifierForS';Prepare the implementation model for a simulation comparison to the baseline results:

Review the automatically generated model and delete vestigial blocks to improve model cleanliness. In this model, the Digial Clock block and the Display block are unnecessary, but they do not inhibit the simulation results.

Right-click the input signal to the Scope block and click Log Signals button .

Note

If your model is too stiff, you may encounter a validation mismatch. To learn about checking the model stiffness, visit Identify and Resolve System Stiffness in Simscape Models.

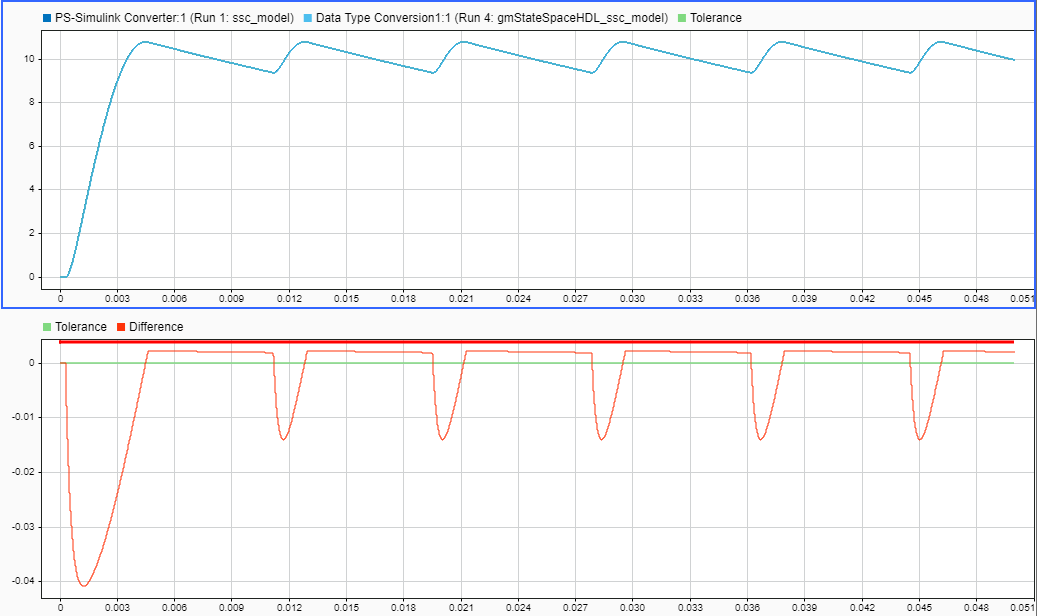

To ensure that the HDL subsystem corresponds to your original Simscape model, simulate the model and compare the results to the baseline simulation results.

sim(HDLmodelname) runIDs = Simulink.sdi.getAllRunIDs; runID1 = runIDs(end - 1); % Baseline model runID2 = runIDs(end); % HDL implementation model run1 = Simulink.sdi.getRun(runID1); run2 = Simulink.sdi.getRun(runID2); sigID1 = getSignalIDByIndex(run1,1); sigID2 = getSignalIDByIndex(run2,1); compBaseline1 = Simulink.sdi.compareSignals(sigID1,sigID2); Simulink.sdi.view

The results are similar to the baseline results. The Simscape model is compatible with HDL code generation.

Generate HDL code from the implementation:

In the HDL implementation model, open the Configuration Parameters window. Expand HDL Code Generation and select Report. Select Generate traceability report and Generate resource utilization report.

Run the

hdlsetupfunction.hdlsetup(HDLmodelname)

### AlgebraicLoopMsg value is set from 'warning' to 'error' (revert). ### BlockReduction value is set from 'on' to 'off' (revert). ### ConditionallyExecuteInputs value is set from 'on' to 'off' (revert). ### DefaultParameterBehavior value is set from 'Tunable' to 'Inlined' (revert). ### FixedStep value is set from 'Auto' to 'auto' (revert). ### InheritOutputTypeSmallerThanSingle value is set from 'off' to 'on' (revert). ### ProdHWDeviceType value is set from '32-bit Generic' to 'ASIC/FPGA->ASIC/FPGA' (revert). ### SingleTaskRateTransMsg value is set from 'none' to 'error' (revert). ### The listed configuration parameter values are modified as a part of hdlsetup. Please refer to hdlsetup document for best practices on model settings.

Save the model and subsystem parameter settings.

hdlsaveparams(HDLmodelname)

%% Set Model 'gmStateSpaceHDL_FullWaveBridgeRectifierForS' HDL parameters hdlset_param('gmStateSpaceHDL_FullWaveBridgeRectifierForS', 'FPToleranceValue', 1.000000e-03); fpconfig = hdlcoder.createFloatingPointTargetConfig('NATIVEFLOATINGPOINT' ... , 'LatencyStrategy', 'Min' ... ); hdlset_param('gmStateSpaceHDL_FullWaveBridgeRectifierForS', 'FloatingPointTargetConfiguration', fpconfig); hdlset_param('gmStateSpaceHDL_FullWaveBridgeRectifierForS', 'HDLSubsystem', 'gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem'); hdlset_param('gmStateSpaceHDL_FullWaveBridgeRectifierForS', 'MaskParameterAsGeneric', 'on'); hdlset_param('gmStateSpaceHDL_FullWaveBridgeRectifierForS', 'Oversampling', 55); hdlset_param('gmStateSpaceHDL_FullWaveBridgeRectifierForS', 'UseFloatingPoint', 'on'); hdlset_param('gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Mode Selection/Generate Mode Vector', 'Architecture', 'MATLAB Datapath'); % Set SubSystem HDL parameters hdlset_param('gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/State Update/Multiply State', 'SharingFactor', 1);Save the validation model generation settings.

hdlset_param(HDLmodelname, 'GenerateValidationModel','on')

Generate HDL code.

makehdl('gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem')### Generating HDL for 'gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem'. ### Using the config set for model gmStateSpaceHDL_FullWaveBridgeRectifierForS for HDL code generation parameters. ### Running HDL checks on the model 'gmStateSpaceHDL_FullWaveBridgeRectifierForS'. ### Begin compilation of the model 'gmStateSpaceHDL_FullWaveBridgeRectifierForS'... ### Begin compilation of the model 'gmStateSpaceHDL_FullWaveBridgeRectifierForS'... ### Working on the model 'gmStateSpaceHDL_FullWaveBridgeRectifierForS'... ### The code generation and optimization options you have chosen have introduced additional pipeline delays. ### The delay balancing feature has automatically inserted matching delays for compensation. ### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays. ### Output port 1: 1 cycles. ### Working on... GenerateModel ### Begin model generation 'gm_gmStateSpaceHDL_FullWaveBridgeRectifierForS' .... ### Rendering DUT with optimization related changes (IO, Area, Pipelining)... ### Model generation complete. ### Generating new validation model: gm_gmStateSpaceHDL_FullWaveBridgeRectifierForS_vnl. ### Validation model generation complete. ### Begin VHDL Code Generation for 'gmStateSpaceHDL_FullWaveBridgeRectifierForS'. ### Unused logic removed during HDL code generation. To highlight the logic removed, click the following MATLAB script: highlightRemovedDeadBlocks.m ### To clear highlighting, click the following MATLAB script: clearHighlightingRemovedDeadBlocks.m ### MESSAGE: The design requires 55 times faster clock with respect to the base rate = 3.33333e-06. ### Begin VHDL Code Generation for 'HDL_Subsystem_tc'. ### Working on HDL_Subsystem_tc as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\HDL_Subsystem_tc.vhd. ### Code Generation for 'HDL_Subsystem_tc' completed. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Mode Selection/Generate Mode Vector/nfp_mul_single as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\nfp_mul_single.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/State Update/nfp_add_single as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\nfp_add_single.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Output/Multiply State/dot_product_2 as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\dot_product_2.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Output as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\Output.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/State Update/Bias as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\Bias.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/State Update/Multiply Input/dot_product_1 as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\dot_product_1.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/State Update/Multiply State/dot_product_1 as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\dot_product_1_block.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/State Update as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\State_Update.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Mode Selection/Generate Mode Vector/nfp_relop_single as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\nfp_relop_single.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Mode Selection/Generate Mode Vector/nfp_uminus_single as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\nfp_uminus_single.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Mode Selection/Generate Mode Vector as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\Generate_Mode_Vector.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Mode Selection as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\Mode_Selection.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Mode Iteration Manager/Counter Limited/Increment Real World as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\Increment_Real_World.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Mode Iteration Manager/Counter Limited/Wrap To Zero as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\Wrap_To_Zero.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Mode Iteration Manager/Counter Limited as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\Counter_Limited.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Mode Iteration Manager/Compare To Constant as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\Compare_To_Constant.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm/Mode Iteration Manager as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\Mode_Iteration_Manager.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem/HDL Algorithm as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\HDL_Algorithm.vhd. ### Working on gmStateSpaceHDL_FullWaveBridgeRectifierForS/HDL Subsystem as hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\HDL_Subsystem.vhd. ### Generating package file hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForS\HDL_Subsystem_pkg.vhd. ### Code Generation for 'gmStateSpaceHDL_FullWaveBridgeRectifierForS' completed. ### Creating HDL Code Generation Check Report HDL_Subsystem_report.html ### HDL check for 'gmStateSpaceHDL_FullWaveBridgeRectifierForS' complete with 0 errors, 3 warnings, and 3 messages. ### HDL code generation complete.

To open the HDL code generation report, click the

HDL_Subsystem_report.htmlhyperlink. The HDL code generation report includes the generated errors or warnings. The report includes a link to the resource utilization report, which describes the resource requirements for FPGA deployment.

The advisor saves the generated HDL code and validation model in the

hdlsrc\gmStateSpaceHDL_FullWaveBridgeRectifierForSdirectory. The generated code file is namedHDL_Subsystem_tc.vhd.

See Also

Functions

hdladvisor(HDL Coder) |hdlsaveparams(HDL Coder) |hdlset_param(HDL Coder) |hdlsetup(HDL Coder) |makehdl(HDL Coder) |simscape.findNonlinearBlocks|sschdladvisor(HDL Coder)