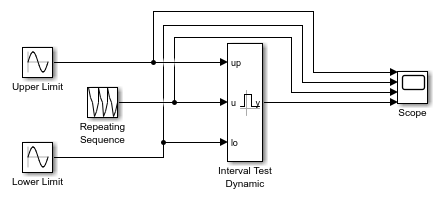

Interval Test Dynamic

确定信号是否在指定区间中

库:

Simulink /

Logic and Bit Operations

描述

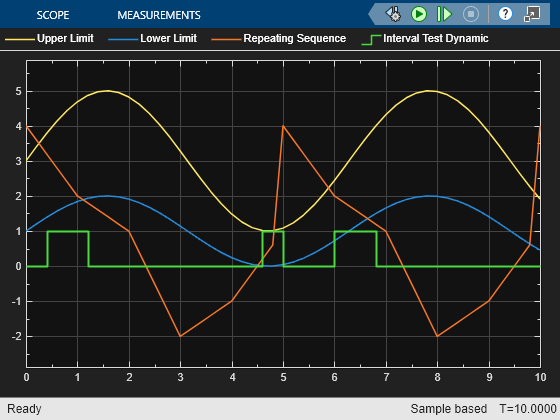

如果输入介于外部信号 up 和 lo 的值之间,则 Interval Test Dynamic 模块输出 true (1)。如果输入在这些值的范围之外,模块将输出 false (0)。要控制模块如何处理等于信号 lo 或信号 up 的输入值,请使用 Interval closed on left 和 Interval closed on right 复选框。

示例

端口

输入

输出

参数

模块特性

数据类型 |

|

直接馈通 |

|

多维信号 |

|

可变大小信号 |

|

过零检测 |

|

扩展功能

版本历史记录

在 R2006a 之前推出