Interval Test

确定信号是否在指定区间中

库:

Simulink /

Logic and Bit Operations

描述

如果输入介于下限和上限指定的值之间,Interval Test 模块将输出 true (1)。如果输入在这些值的范围之外,模块将输出 false (0)。当输入等于下限或上限时,模块的输出取决于您是选中左半闭区间还是右半闭区间复选框。

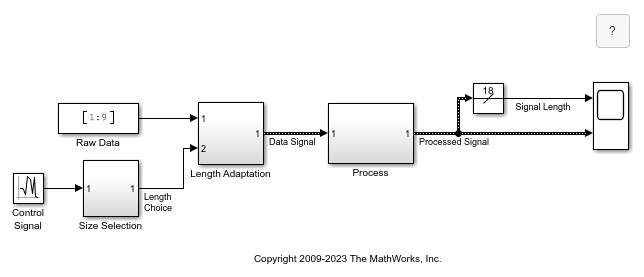

示例

端口

输入

输入信号,指定为标量、向量、矩阵或 N 维数组。

限制

当输入信号为枚举类型时,上限和下限值必须具有相同的枚举类型。

数据类型: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point | enumerated

输出

指示输入值是否在指定区间内的输出信号。您可以将输出数据类型指定为 boolean 或 uint8。

数据类型: uint8 | Boolean

参数

当选中此复选框时,上限包括在模块对其输出 true (1) 的区间中。

编程用法

模块参数: IntervalClosedRight |

| 类型:字符向量 |

值:'on' | 'off' |

默认值:'on' |

模块对其输出 true (1) 的区间的上限值。

编程用法

模块参数:uplimit |

| 类型:字符向量 |

| 值:标量 | 向量 | 矩阵 | N 维数组 |

默认值:'0.5' |

当选中此复选框时,下限包括在模块对其输出 true (1) 的区间中。

编程用法

模块参数: IntervalClosedLeft |

| 类型:字符向量 |

值:'on' | 'off' |

默认值:'on' |

模块对其输出 true (1) 的区间的下限值。

编程用法

模块参数:lowlimit |

| 类型:字符向量 |

| 值:标量 | 向量 | 矩阵 | N 维数组 |

默认值:'-0.5' |

将输出数据类型指定为 boolean 或 uint8。

编程用法

模块参数:OutDataTypeStr |

| 类型:字符向量 |

值:'boolean' | 'uint8' |

默认值:'boolean' |

模块特性

数据类型 |

|

直接馈通 |

|

多维信号 |

|

可变大小信号 |

|

过零检测 |

|

扩展功能

C/C++ 代码生成

使用 Simulink® Coder™ 生成 C 代码和 C++ 代码。

HDL Coder™ 提供影响 HDL 实现和综合逻辑的额外配置选项。

| 架构 | 描述 |

|---|---|

| 模块(默认值) | 为子系统和子系统内的模块生成代码。 |

| BlackBox | 生成黑盒接口。生成的 HDL 代码仅包括子系统的输入/输出端口定义。因此,您可以在模型中使用子系统来生成与手动编写的现有 HDL 代码的接口。 子系统的黑盒接口生成类似于没有时钟信号的 Model 模块接口生成。 |

无 HDL | 从生成的代码中删除子系统。您可以在仿真中使用子系统,但在 HDL 代码中将其视为“无操作”。 |

对于 BlackBox 架构,您可以自定义端口名称并设置外部组件接口的属性。请参阅Customize Black Box or HDL Cosimulation Interface (HDL Coder)。

| 通用 | |

|---|---|

| AdaptivePipelining | 基于综合工具、目标频率和乘法器字长的自动流水线插入。默认值为 inherit。另请参阅AdaptivePipelining (HDL Coder)。 |

| ClockRatePipelining | 以较快的时钟频率而不是较慢的数据速率插入流水线寄存器。默认值为 inherit。另请参阅ClockRatePipelining (HDL Coder)。 |

| ConstrainedOutputPipeline | 通过移动设计中现有延迟的方式来放置在输出端的寄存器的数量。分布式流水线不会重新分发这些寄存器。默认值为 |

| DistributedPipelining | 流水线寄存器分配或寄存器重定时。默认值为 inherit。另请参阅DistributedPipelining (HDL Coder)。 |

| FlattenHierarchy | 从生成的 HDL 代码中删除子系统层次结构。默认值为 inherit。另请参阅FlattenHierarchy (HDL Coder)。 |

| InputPipeline | 要在生成的代码中插入的输入流水线阶段数。分布式流水线和受限输出流水线可以移动这些寄存器。默认值为 |

| OutputPipeline | 要在生成的代码中插入的输出流水线阶段数。分布式流水线和受限输出流水线可以移动这些寄存器。默认值为 |

| SharingFactor | 要映射到单个共享资源的功能等效的资源的数量。默认值为 0。另请参阅Resource Sharing (HDL Coder)。 |

| StreamingFactor | 并行数据路径或向量的数量,这些路径或向量通过时间多路复用的方式变换为串行标量数据路径。默认值为 0,表示实现完全并行的数据路径。另请参阅Streaming (HDL Coder)。 |

| SynthesisAttributes | 指定模型中模块和模块输出信号的综合属性。生成的 HDL 代码包含这些属性。有关详细信息,请参阅SynthesisAttributes (HDL Coder)。 |

如果此模块不是 DUT,将忽略目标设定选项卡中的模块属性设置。在 HDL 工作流顾问中,如果您使用 IP 核生成工作流,这些目标设定模块属性值将随模型一起保存。如果您使用 hdlset_param 指定这些目标设定模块属性值,则当您打开 HDL 工作流顾问时,系统将使用对应的值填充这些字段。

| 目标设定 | |

|---|---|

| AdditionalTargetInterfaces | 附加目标接口,指定为字符向量。 要在模型上保存此模块属性,请在 IP 核生成工作流的设置目标接口任务中,对应于您要添加更多接口的 DUT 端口,选择 Add more...。然后,您可以在“添加新目标接口”对话框中添加更多接口。指定接口类型、附加接口数量以及每个附加接口的唯一名称。 值: 示例: |

| ProcessorFPGASynchronization | 处理器/FPGA 同步模式,指定为字符向量。 要在模型上保存此模块属性,请在 IP 核生成工作流的设置目标接口任务中指定处理器/FPGA 同步。 值: 示例: |

| TestPointMapping | 要在模型上保存此模块属性,请在 IP 核生成工作流的设置目标接口任务中指定测试点端口到目标平台接口的映射。 值: 示例: |

| TunableParameterMapping | 要在模型上保存此模块属性,请在 IP 核生成工作流的设置目标接口任务中指定可调参数端口到目标平台接口的映射。 值: 示例: |

| WriteRegisterReadback | 要在模型上保存此模块属性,请在 IP 核生成工作流的生成 RTL 代码和 IP 核任务中指定是否对写寄存器(例如 AXI4 从属站接口)启用读回。要了解详细信息,请参阅Model Design for AXI4 Register Interface Generation (HDL Coder)。 值: |

| AXI4SubordinateIDWidth | 要在模型上保存此模块属性,请使用 IP 核生成工作流的生成 RTL 代码和 IP 核任务中的 AXI4 从设备 ID 宽度设置,指定要将 DUT IP 核连接到的 AXI 主设备接口的数量。要了解详细信息,请参阅Define Multiple AXI Master Interfaces in Reference Designs to Access DUT AXI4 Subordinate Interface (HDL Coder)。 值: |

| RegisterInterfaceReadPipeline | 要在模型上保存此模块属性,请使用 IP 核生成工作流的生成 RTL 代码和 IP 核任务中的寄存器接口读取流水线设置,指定要在读取地址解码器路径中插入的流水线阶段数。要了解详细信息,请参阅Model Design for AXI4 Register Interface Generation (HDL Coder)。 值: |

| GenerateDefaultRegisterInterface | 要在模型上保存此模块属性,请在 IP 核生成工作流的生成 RTL 代码和 IP 核任务中指定是否要禁用默认寄存器接口(例如 AXI4 从设备接口)的生成。 值: |

| IPCoreAdditionalFiles | 设计中黑盒的 Verilog®、SystemVerilog 或 VHDL® 文件。指定每个文件的完整路径,并用分号 (;) 分隔各文件名。 您可以在 HDL 工作流顾问的其他源文件字段中设置此属性。 值: 示例: |

| IPCoreName | IP 核名称,指定为字符向量。 您可以在 HDL 工作流顾问的 IP 核名称字段中设置此属性。如果将此属性设置为默认值,HDL 工作流顾问将基于 DUT 的名称构造 IP 核名称。 值: 示例: |

| IPCoreVersion | IP 核版本号,指定为字符向量。 您可以在 HDL 工作流顾问的 IP 核版本字段中设置此属性。如果此属性设置为默认值,则 HDL 工作流顾问将设置 IP 核版本。 值: 示例: |

| IPDataCaptureBufferSize | FPGA 数据采集缓冲区大小,指定为字符向量。当在 FPGA 上运行时,请使用 FPGA 数据采集来观察设计中的信号。 缓冲区大小的值为 128*2^n,其中 n 是整数。默认情况下,缓冲区大小为 128 (n=0)。n 的最大值是 13,即缓冲区大小的最大值是 1048576 (=128*2^13)。 值: 示例: |

| IPCoreVendorName | IP 核供应商名称,指定为字符向量。 您可以在 HDL 工作流顾问中通过在 IP 核供应商名称字段中输入值来设置此属性。如果此属性设置为默认值,则 HDL 工作流顾问会将供应商名称设置为您的主机的域名。 供应商名称不能以数字字符开头(例如, 值: 示例: |

PLC 代码生成

使用 Simulink® PLC Coder™ 生成结构化文本代码。

定点转换

使用 Fixed-Point Designer™ 设计和仿真定点系统。

版本历史记录

在 R2006a 之前推出

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

选择网站

选择网站以获取翻译的可用内容,以及查看当地活动和优惠。根据您的位置,我们建议您选择:。

您也可以从以下列表中选择网站:

如何获得最佳网站性能

选择中国网站(中文或英文)以获得最佳网站性能。其他 MathWorks 国家/地区网站并未针对您所在位置的访问进行优化。

美洲

- América Latina (Español)

- Canada (English)

- United States (English)

欧洲

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)